單片機+CPLD的多路精確延時控制系統

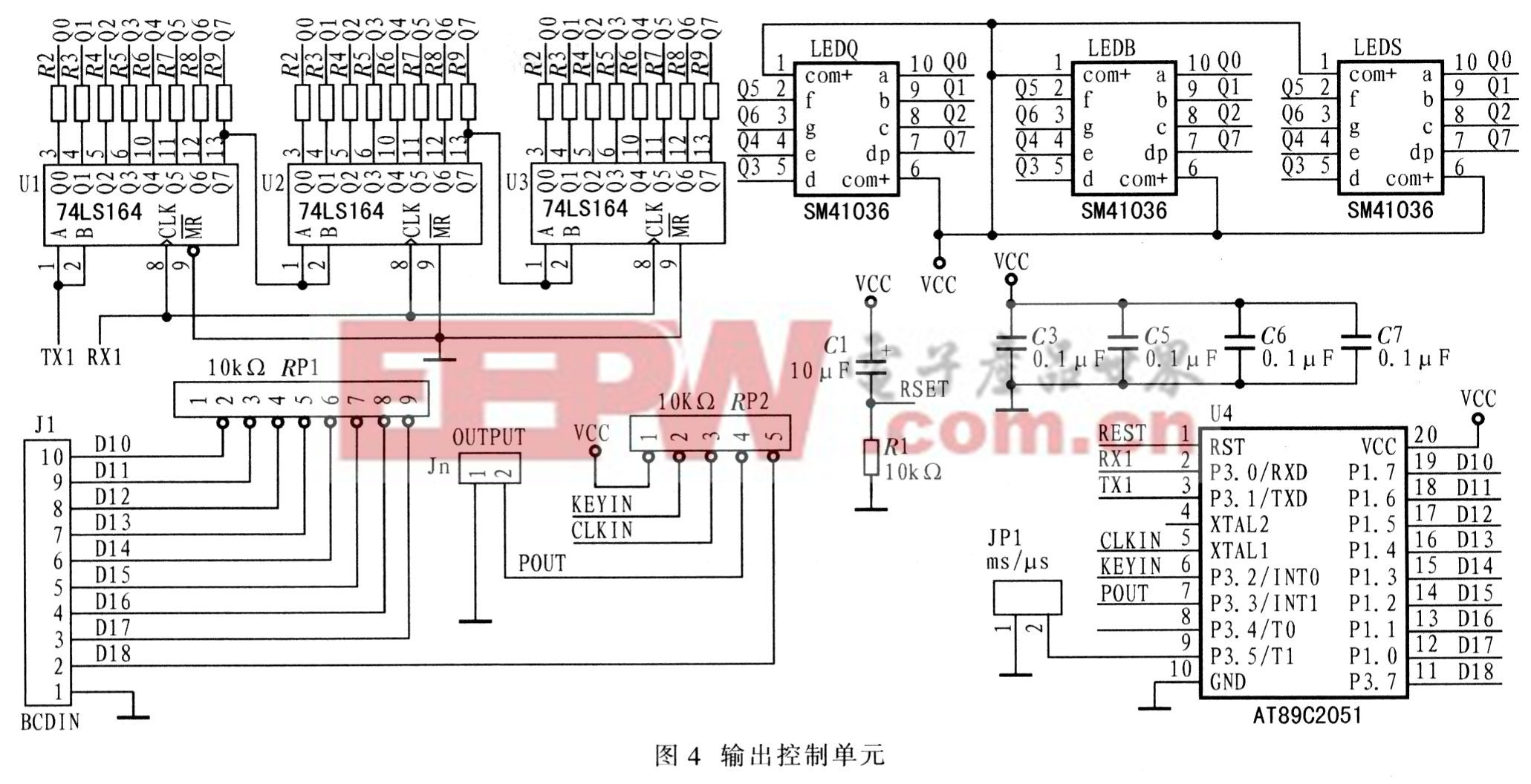

每個系統由n(本系統設計中n=9)個輸出控制單元組成,這n個單元輸出控制獨立并行工作,如圖4所示。N0.1~N0.n以ATMEL公司5l系列單片機AT89C2051為核心。AT89C205l是低功耗、高性能CMOS 8位單片機,具有15個雙向輸入/輸出(I/O)端口、片內含2 K字節的可反復擦寫的只讀Flash程序存儲器和128字節的隨機存取數據存儲器(RAM);采用ATMEL公司的高密度、非易失性存儲技術生產,兼容標準MCS一5l指令系統。輸出控制單元(NO.1~NO.n)并行工作,完成延時時間設置、μs/ms變換設置、控制信號輸出和延時顯示等功能,延時時間顯示通過單片機串口實現,由3片串/并變換器件74LSl64驅動3個共陽數碼管。本文引用地址:http://www.104case.com/article/162113.htm

4 系統軟件設計

本系統軟件設計包括CPUO單元、NO.1~NO.n輸出單元及CPLD單元程序設計。由于對時間要求嚴格,采用匯編語言編寫,信號輸出由中斷程序完成,由于中斷響應過程、現場保護以及中斷后必要的設置條件檢測需要時間,所以軟件必須通過容余指令(比如NOP)的延時,可保證counter0輸出和控制信號延時起點在同一時刻。

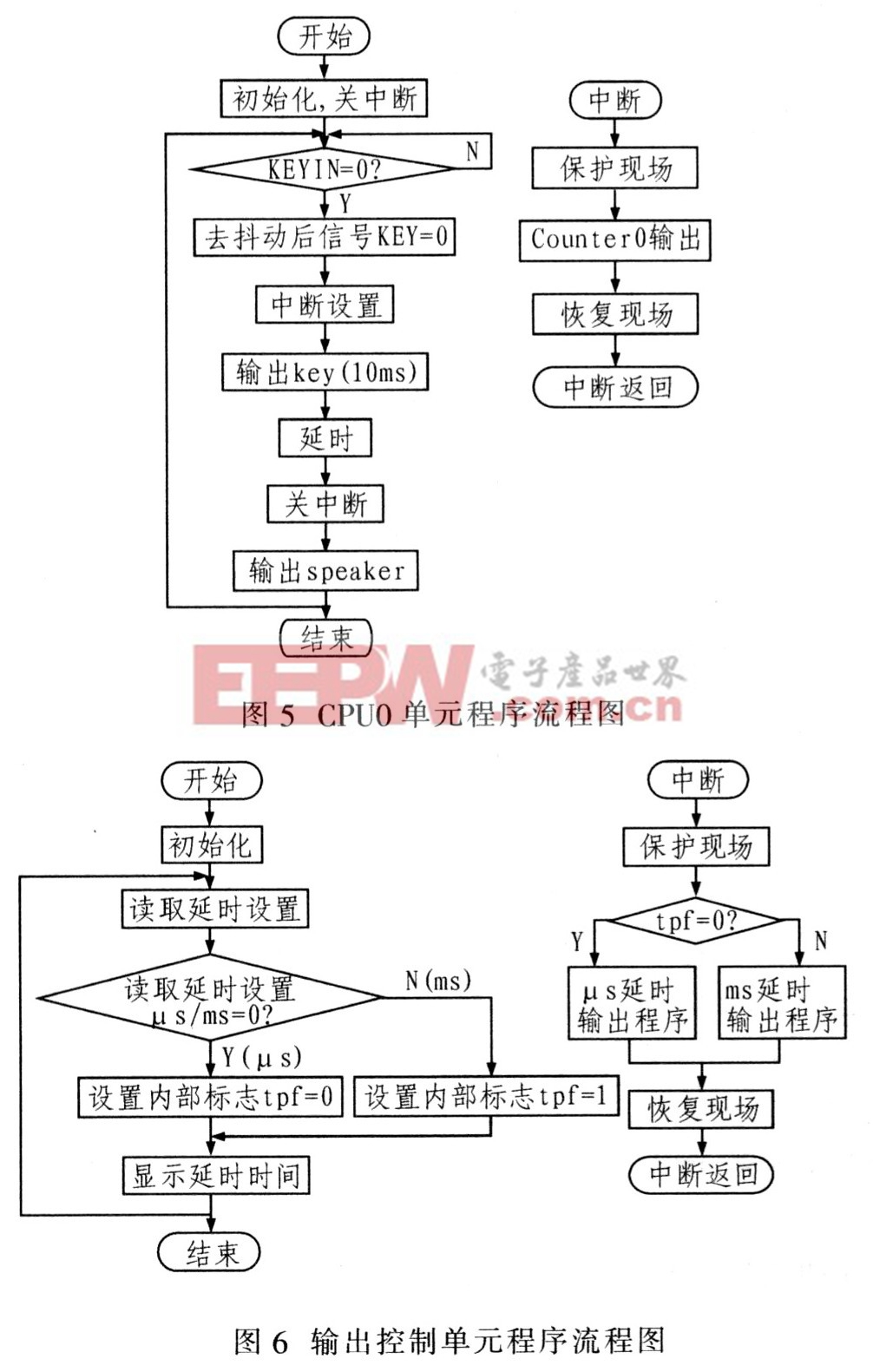

CPU0單元程序流程如圖5所示。CPU0主程序完成系統初始化、按鍵檢測、去抖動信號輸出和工作狀態提示音輸出等工作,中斷服務程序計時基準信號counterO輸出。輸出控制單元NO.1一NO.n程序流程如圖6所示,各單元主程序完成μs/ms設置檢測,延時設置讀取,延時時間顯示,中斷程序完成控制信號輸出功能。CPLD程序采用VHDL語言編寫,采用QHalftusⅡ軟件編譯仿真。

5 結語

該系統設計可應用于電容組(9只)放電控制系統,在放電電子開關控制端、

評論