發射應用中多個高速、復用DAC的同步

本文引用地址:http://www.104case.com/article/161853.htm

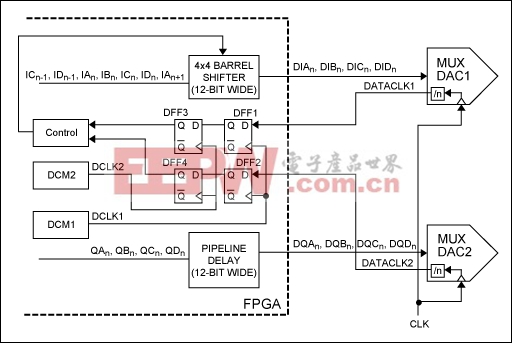

通過輸入數據移位實現DAC相位調整

可以利用Xilinx® FPGA中先進的數字時鐘管理程序(DCM)來檢測兩個MUX-DAC的數據時鐘之間的相位差異(圖6)。DCM1生成一個與DATACLK1和DATACLK2相同頻率的時鐘。以時鐘周期的1/256為間距對DCLK1的延遲進行動態調整。觸發器DFF1和DFF2在每個時鐘周期對DATACLK1和DATACLK2進行一次采樣。如果DFF1在DATACLK1為低時采樣DATACLK1,DFF1會輸出固定的“0”。如果DFF1在DATACLK1為高時采樣DATACLK1,DFF1會輸出固定的“1”。所以DFF3和DFF4可在任意時鐘相位定時,與DCLK1的延遲設置無關。通過將DCLK1的延遲進行分級,使用DCM1的動態延遲調整功能以及讀取DFF3和DFF4的輸出,我們可以得到基于DATACLK1和DATACLK2上升沿的延遲設置。根據延遲設置,我們可以計算出為了保持MUX-DAC1和MUX-DAC2輸入數據的同相,MUX-DAC1的輸入數據需要延遲的DAC時鐘周期數。FPGA中4 x 4桶形移位器的實現可使數據等待時間以一個DAC時鐘周期為增量進行改變(參見圖6)。

MAX19692有四個并行數據端口A、B、C和D。輸入DAC的數據序列是An、Bn、 Cn、Dn、An+1、Bn+1、Cn+1、Dn+1、An+2等。12位4 x 4柱形移位器(圖6)允許輸入MUX-DAC1的數據延遲-1、0、1或2個CLK周期。因此可以進行數據等待時間的調整直到兩個DAC的輸出數據同相。這樣的話,兩個DAC的數據時鐘可能相距幾個整數時鐘(CLK)周期且不再改變。由于DAC的建立和保持時間以數據時鐘為基準,所以兩個DAC的數據時序必須不同。可以通過驅動DAC的FPGA中的多個DCM來實現。

圖6. 利用FPGA中桶形移位器的實現完成MUX-DAC的同步

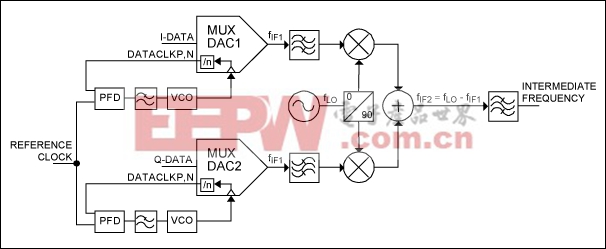

每個DAC使用一個PLL實現DAC同步

如果DAC使用鎖相環(PLL)合成器來定時,那么同步兩個DAC的方法就是每個DAC使用單獨的PLL (圖7)。DAC1和DAC2的LVDS數據時鐘輸出相位與參考時鐘相比較。這樣的話,DAC的內部時鐘分頻器在時鐘生成PLL中作為反饋分頻器使用。

圖7. 每個DAC使用一個PLL實現MUX-DAC同步

這種方法中,兩個DAC的建立和保持時間相匹配。但是這種方法有兩個缺點,兩個PLL會帶來額外的成本且PLL的相位噪聲極限可能會造成性能極限。

結論

MAX19692為2.3Gsps、12位、可工作于多個奈奎斯特頻帶內的DAC,具有集成的4:1輸入數據多路復用器,是I/Q應用中的理想器件。當I/Q應用中MAX19692的使用被強調時,所討論的方案同樣適用于其它DAC和應用,比如在多于兩個通道應用中使用的MAX5858A。本文所推薦的方案適用于任意數量的DAC。為了對高速器件進行正確的同步,還必須考慮與電路板引線相關的延遲。

評論