基于FPGA和USB 2.0的數(shù)字圖像采集系統(tǒng)設(shè)計

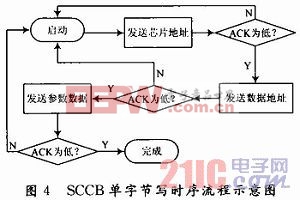

程序中使用順序的方式,將要發(fā)送的數(shù)據(jù)逐位發(fā)送的方式來進(jìn)行設(shè)置,其狀態(tài)機如圖4所示。本文引用地址:http://www.104case.com/article/161153.htm

將要初始化的寄存器地址以及所要設(shè)置的值直接存放于parameter定義的參數(shù)中;在上電時,通過I2C程序?qū)⑦@些寫到OV7620當(dāng)中,實現(xiàn)圖像傳感器的初始化工作。

3 CY7C68013A芯片SLAVE FIFO模式固件編寫

由于系統(tǒng)用于圖像的采集,具有數(shù)據(jù)量大,實時性要求高的特點,因此采用USB 2.0接口,以便能滿足實時,高速的數(shù)據(jù)傳輸。為了達(dá)到最快的傳輸速率,使用SLAVE FIFO模式,在該模式下,USB芯片的數(shù)據(jù)傳輸不需要8051的參與,便于大量連續(xù)的數(shù)據(jù)傳輸,在這種模式下需要有一個外部的控制時序,而FPGA恰能提供相關(guān)的時序,同時為了能夠與圖像數(shù)據(jù)同步,采用外部輸入時鐘,同步傳輸方式,采用8位數(shù)據(jù)傳輸。在該應(yīng)用中,寄存器EP2CFG配置了端點2作為IN端點傳輸FPGA來的數(shù)據(jù)至上位機,寄存器EP2FIFOCFG使能自動傳輸;寄存器EP6CFG配置端點6為OUT端點,寄存器EP6FIFOCFG使能自動傳輸;并在寄存器FIFOPINPOLAR中設(shè)置了端點的滿標(biāo)志為高電平有效,這是由于在剛上電下載完FPGA程序后,F(xiàn)PGA即對圖像進(jìn)行采集并存儲至SRAM當(dāng)中,而上電時FPGA的引腳默認(rèn)為高電平,如果沒有設(shè)置高電平為EP2的滿有效,則在下載USB固件之前FPGA會誤認(rèn)為是USB的端點一直處于非滿狀態(tài)而一直傳送數(shù)據(jù),這樣,在下載完USB固件后,主機端所得到的圖像就不能保證它是從一幀圖像的第一個數(shù)據(jù)開始傳輸而是與下一幀的圖像有一定的錯位。在設(shè)置EZ-USB FX2LP為SLAVE FIFO模式的過程大致是:配置IFCONFIG[1:0]=11,先把SLAVE FIFO模式;復(fù)位相應(yīng)端點,即使用FIFOREST寄存器;配置所要用的端點大小,類型,以及傳輸方向,使用EPxCFG,式中x代表2,4,6,8;設(shè)置各端點的空標(biāo)志,滿標(biāo)志和可編程標(biāo)志值,使用PINFLAGAB和PINFLAGCD寄存器;配置是否使能自動傳輸以及傳輸?shù)奈粚挘褂肊PxFIFOCFG,式中x代表2,4,6,8;本應(yīng)用中的USB固件程序的部分代碼如下:

4 FPGA對圖像數(shù)據(jù)的采集、存儲及對USB的傳輸控制

4.1 FPGA對圖像的采集控制

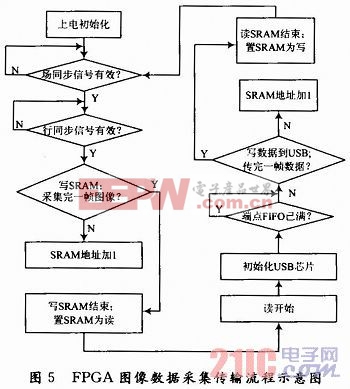

FPGA對圖像的采集控制是通過OV7620的VSYNC,HREF,PCLK三個源同步時序信號來對圖像進(jìn)行采集。首先是在1個狀態(tài)機中檢測VSYNC信號,當(dāng)VSYNC的高電平來臨時,初始化所有的內(nèi)部寄存器,包括SRAM的地址寄存器,SRAM的寫控制信號,數(shù)據(jù)總線讀寫方向的選擇信號,USB的寫使能信號,內(nèi)部計數(shù)寄存器等;等VSYNC來臨之后,表示新的一幀開始了,接下來等待圖像的行信號使能來臨,當(dāng)HREF到來之后,就可以將圖像的數(shù)據(jù)寫進(jìn)SRAM當(dāng)中了,這個寫過程需要兩個CLK,在第一個時鐘周期中更改SRAM的寫地址,第2個CLK周期將連接在數(shù)據(jù)總線上的圖像數(shù)據(jù)寫進(jìn)SRAM中,同時對內(nèi)部的圖像計數(shù)器進(jìn)行計數(shù),這個過程中要在HREF為高電平的時候進(jìn)行存儲;當(dāng)計數(shù)達(dá)到一幀,也就是153 600 B的時候結(jié)束采集的過程,并更改相應(yīng)的控制信號,準(zhǔn)備USB的操作信號,進(jìn)行FPGA對USB芯片的控制,將SRAM當(dāng)中的一幅完整的圖像能過USB傳至USB當(dāng)中,整個采集與傳送的狀態(tài)流程如圖5所示。

4.2 FPGA對USB芯片的控制

在FPGA完成了一幅圖像的采集并將圖像的數(shù)據(jù)存儲在片外的SRAM當(dāng)中以后,接下來要做的事情就是將所存儲的圖像傳給USB芯片,這個過程當(dāng)中,F(xiàn)PGA要控制SRAM的寫信號,同時使能數(shù)據(jù)總線的方向為輸出方向。FPGA對USB的寫首先是花費一個CLK的時間從SRAM當(dāng)中取出一個數(shù)據(jù),之后在第2個CLK時間內(nèi)判斷它的端點滿標(biāo)志,如果USB端點已經(jīng)滿了,則等待,如果非滿,則拉低寫信號使能信號同時地址計數(shù)器加1,返回上一個取數(shù)據(jù)的狀態(tài)繼續(xù)取下一個數(shù)據(jù),直到傳完一幅圖片,之后返回初始的狀態(tài)重新等新的一幀開始信號的到來。

評論