高速同步數據采集平臺的實現

2.1 高速數據合并器

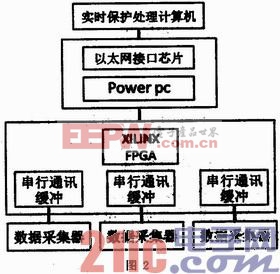

數據合并器的主要工作是產生同步信號,并對64路高速串行上傳數據進行同時的接收、合并,并通過以太網實時上傳。因此主要有以下性能需求:同步信號的產生;多路高速數圖1據接收,64路每路數據流為1638400bit/s;多路高速數據接收下來后以以太網實時上傳,速度是25Mbit/s。

項目采用以下解決方案:

(1)同步信號的產生由單獨的MCU處理器來實現,其不僅產生同步信號,同時負責相關數據協議的處理。

(2)高速數據的接收,需要用FPGA的同步處理能力,單獨設置64個串行接口模塊,分別接收緩沖的高速數據。

(3)高速數據上傳也要通過FPGA實現對接收到的數據實時上傳至XILINX的XC3S4000來實現。

整個系統的硬件框圖如圖2所示。本文引用地址:http://www.104case.com/article/159579.htm

2.2 傳感器數據采集器

傳感器數據采集器的主要功能是接收合并器的同步時鐘信號,并利用AD對傳感器信號進行采集,按自定協議將數據通過光纖上傳至合并器。主要的指標如下:采樣頻率為每秒12800次(12.8kHz);每終端需要同時采集8路傳感器信號,每信號不低于16位。

采用TMS320F2812的串口來實現同步信號的接收與采集。8路同步采集用8個16位AD來實現。

與合并器的數據通訊同樣要考慮光纖模塊,考慮保證AD轉換16位的精度,所以選擇ADS8342。在以上硬件的基礎上,系統利用軟件完成對傳感器的高速數據采集。

3 系統軟件部分說明

整個系統的軟件組成主要在三個不同設備上實現,一是基于工業計算機板卡的wince上的中心數據處理控制程序,主要實現對采集后的數據的處理運算,并下發控制指令,二是基于XINLINX的FPGA平臺的數據匯總程序與指令下發程序,三是基于DSP 2812的數據采集終端部分的數據采集、上傳、指令接收等程序。

3.1 數據合并器同步與數據采集程序

數據合并器是對采集器進行下行通訊管理的通道,主要負責產生同步信號的,收集串口數據上傳等功能。其中下行信息主要有同步采集時鐘信號、時間校準信息、控制信息,以及參數信息。其中以同步采集時鐘最為關鍵,主要是要給采集器一個統一的采集節拍。

對于上行數據而言,采用FIFO原理,將所有的串口緩存進行緩沖,并形成一個按協議要求的數據包,從而實現數據的統一上傳。FIFO原理從硬件的角度來看,是一塊有兩個端口的數據內存,一個端口用來寫入數據;另一個用來讀出數據。與FIFO操作相關的有兩個指針,寫指針指向要寫的內存部分,讀指針指向要讀的內存部分。FIFO控制器通過外部的讀寫信號控制這兩個指針移動,并由此產生FIFO空信號或滿信號。數據是由某一個時鐘域的控制信號寫入FIFO,而由另一個時鐘域的控制信號將數據讀出FIFO。

評論