CAN協議中CRC編碼的硬件實現

關鍵詞 CAN協議;CRC檢驗;串行;并行

1 引言

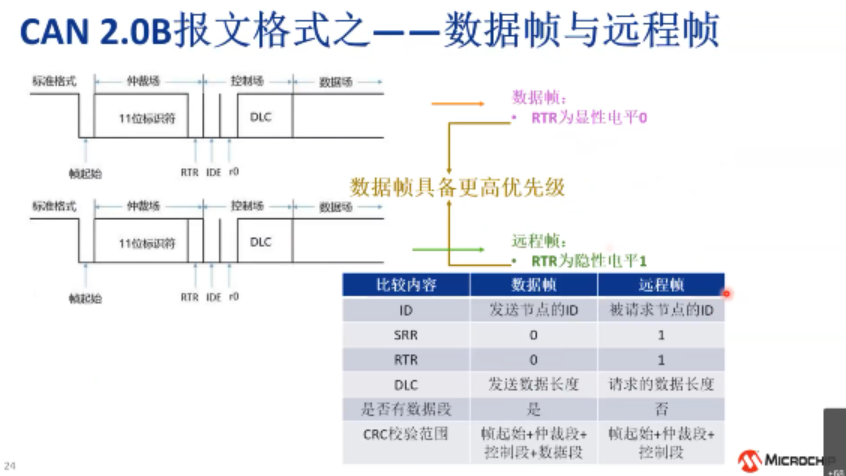

通信系統總線在傳輸信息時,不可避免要受到各種干擾的影響,使得傳輸信息出錯。CAN協議中,為了保證幀傳輸的可靠性和較高的檢錯效率,其采用了以下幾種檢錯方式:位錯誤、填充錯誤、CRC錯誤、格式錯誤及應答錯誤檢測。通過以上檢錯方式,它對于受損報文檢測不到其受損的概率為:報文受損率*4.7*10-11,因而CAN總線極高的檢錯率使得它目前被廣泛應用到工業控制、通信、汽車甚至軍事等多個領域。CRC檢驗作為CAN協議中一種重要的且行之有效的檢錯方式,它的生成多項式可以檢驗7級,具有編碼簡單且誤判率低的優點。

2 CRC檢驗原理

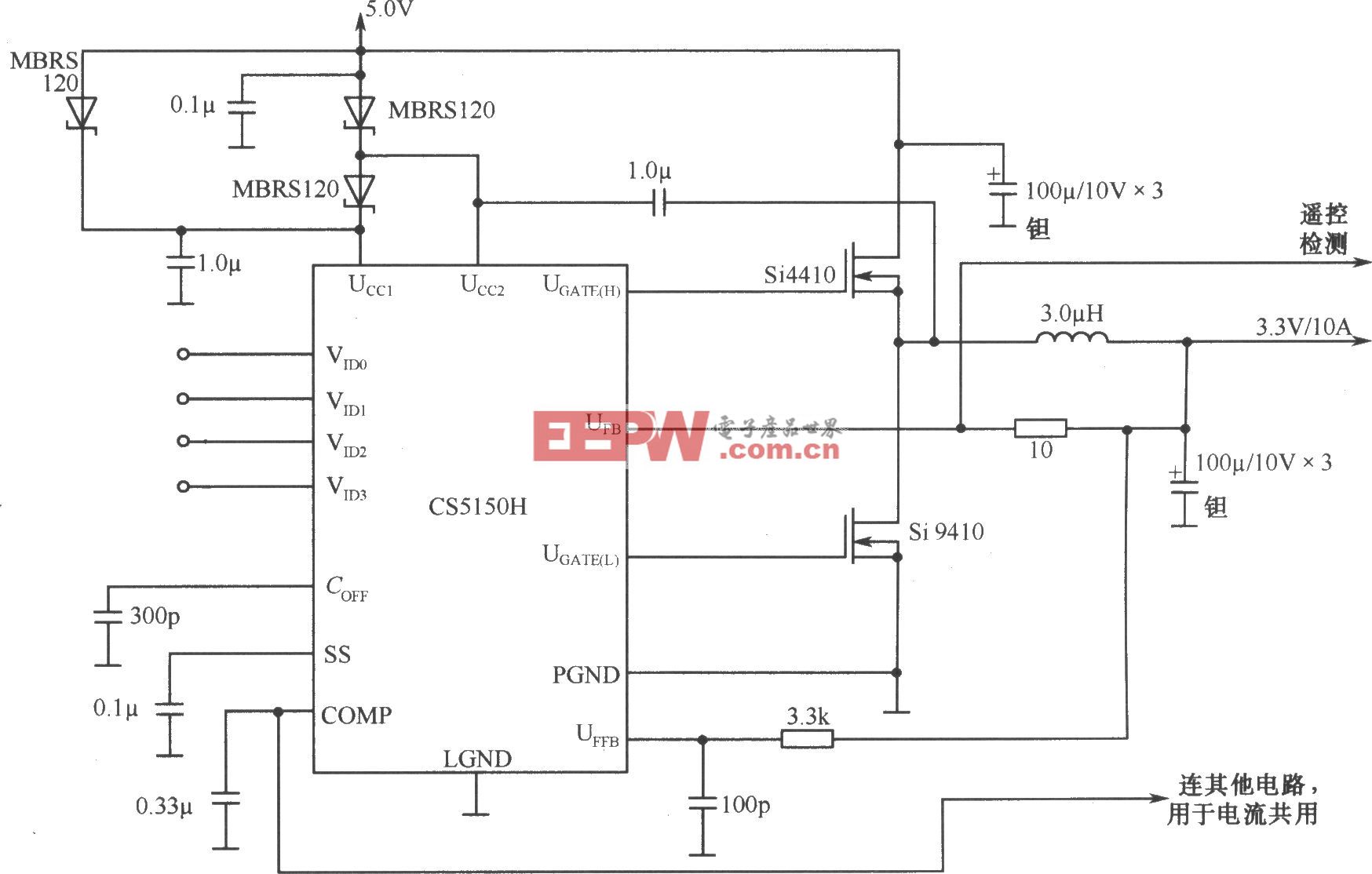

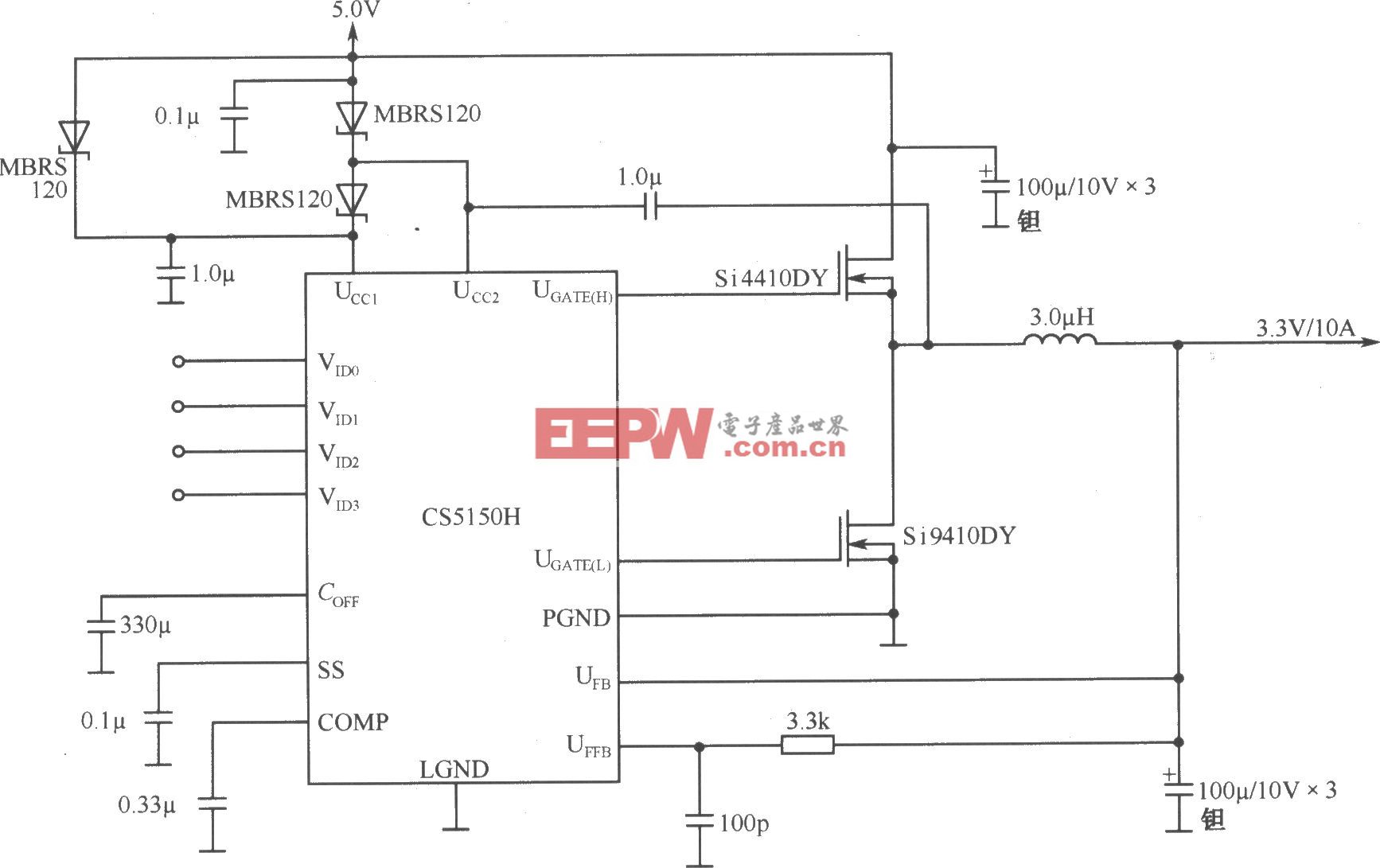

CAN協議中規定,需要對幀起始、仲裁場、控制場和數據場(若存在的話)組成的未經填充的位流進行CRC編碼。具體實現方法為:被除多項式的系數由幀起始、仲裁場、控制場、數據場(若存在的話)及15位(最低系數)0組成的未經填充的位流給定,而生成多項式為X15+X14+X10+X8+X7+X4+X3+1,被除多項式被生成多項式除(系數按模-2計算),余數即為將要發至總線的CRC序列。發送節點和接收接點的CAN控制器均采用相同的方法生成CRC檢驗碼,并與發送節點送出的CRC檢驗碼進行比較,以判斷報文是否出錯,若出錯,CAN控制器會依據總線仲裁原則及受損報文優先發送原則對已損壞報文自動進行重發。

3 CRC檢驗碼電路的硬件實現

CRC檢驗碼硬件上的實現,可以采用串行和并行兩種實現方式。在串行方式中,需編碼的位流按位逐位輸入,位流輸入完成后生成檢驗碼,檢驗碼緊隨需檢驗的位流發出或接收到。并行方式中需檢驗的位流每k位輸入到檢驗碼生成電路中,因而檢驗碼的生成效率大大高于串行方式。以下針對CAN 協議中CRC檢驗的生成多項式進行闡述。

3.1 CRC檢驗碼的串行實現

CAN協議中CRC碼為15位,需要15位的移位寄存器來實現,移位寄存器c0c1c2……c12c13c14在CRC檢驗碼生成過程中寄存CRC檢驗碼的中間值,計算完成后其值即為最終的CRC檢驗碼。設c(t)=[c0c1c2……c12c13c14]為t時刻移位寄存器的狀態,復位時初始狀態時c(0)=[ 000……000]。移位寄存器的狀態轉換方程為:

c(t+1)= [c0c1c2……c12c13]*[0|I14](c14dst)*g

= [c0c1c2……c12c13]*[0|I14]c14*gdst*g

= [c0c1c2……c12c13 c14]*Adst*g

= c(t) *Adst*g

上式中,I14為14階單位陣,dst為串行輸入數據,表示異或,g=[g0g1……g13g14]為生成多項式的系數行矩陣,而A為n階方陣 。

。

。

。 依據以上的CRC檢驗碼的狀態轉換方程實現的RTL級的VHDL代碼如下:

c=ds xor c(14);

if(rst='0')then

c=(others=>'0');

elsif(rising_edge(clk))then

if(en_transmit='0')then

c=(others=>'0');

elsif(en_crc_code='1' and f_ds='1' and f_ds_sync='0')then

if(c ='1')then

c(14 downto 1)=c(13 downto 0) xor "10001011001100";

c(0)='1';

else

c(14 downto 1)=c(13 downto 0);

c(0)='0';

end if;

end if;

end if;

在以上代碼中,rst 為外部復位信號,en_transmit 為幀發送使能信號,en_crc_code 為CRC代碼編碼使能信號,ds為輸入的串行數據,f_ds與ds同時有效,f_ds='1' and f_ds_sync='0'代表f_ds的上升沿,c為15位移位寄存器,用于寄存CRC檢驗碼的中間結果并輸出其最終結果。

需注意的是:信號en_crc_code在發送支路中和接收支路中應包含需編碼位流的填充和解除填充信息(即填充位不進行編碼)。

3.2 CRC檢驗碼的并行實現

CRC檢驗碼的并行實現方式,CAN協議中未給出,但并行實現方式具有很高的檢驗碼生成效率,很有必要采用,以下給出其實現方法。其狀態轉移方程可表示為:

式中,c為15位移位寄存器,復位時各位均為0,在檢驗碼生成過程中,寄存CRC檢驗碼的中間值,其值每輸入k位數據變化一次,編碼完成后輸出最終的檢驗碼,c(t)和c(t+k)分別為c在t時刻及t+k時刻的狀態,實際應用中c(t+k)表示緊隨c(t)狀態的并行k位數據輸入后的狀態,k 為并行寬度,此處取8,dp為k位并行輸入數據,A即為3.1節所述方陣,

,其中的G亦為3.1節所述的生成多項式的系數行矩陣。矩陣運算過程中, 需注意的是:矩陣乘積的結果需進行模2處理,即奇數用1代替,偶數以0代替。由此得到基于CAN協議中生成多項式的8位并行CRC檢驗碼邏輯表,如表1所示。寄存器每位的表示如c6= c9c13dp2dp6。在實際編碼中,需添加一些控制信號,如異步復位信號、編碼同步清零信號、編碼同步使能信號等。

,其中的G亦為3.1節所述的生成多項式的系數行矩陣。矩陣運算過程中, 需注意的是:矩陣乘積的結果需進行模2處理,即奇數用1代替,偶數以0代替。由此得到基于CAN協議中生成多項式的8位并行CRC檢驗碼邏輯表,如表1所示。寄存器每位的表示如c6= c9c13dp2dp6。在實際編碼中,需添加一些控制信號,如異步復位信號、編碼同步清零信號、編碼同步使能信號等。表1 8位并行CRC檢驗碼邏輯表

c(t+k) | c(t)、dp |

c0 | c7 c8 c9 c10 c11 c13 c14 dp 0 dp1 dp2 dp3 dp4 dp6 dp7 |

c1 | c8 c9 c10 c11 c12 c14 dp1 dp2 dp3 dp4 dp5 dp7 |

c2 | c9 c10 c11 c12 c13 dp2 dp3 dp4 dp5 dp6 |

c3 | c7 c8 c9 c12 dp0 dp1 dp2 dp4 |

c4 | c7 c11 c14 dp4 dp7 dp10 |

c5 | c8 c12 dp1 dp5 |

c6 | c9 c13 dp2 dp6 |

c7 | c7 c8 c9 c11 c13 dp0 dp1 dp2 dp4 dp5 |

c8 | c0 c7 c11 c12 c13 dp0 dp4 dp5 dp6 |

c9 | c1 c8 c12 c13 c14 dp1 dp5 dp6 dp7 |

c10 | c2 c7 c8 c10 c11 dp0 dp1 dp3 dp4 |

c11 | c3 c8 c9 c11 c12 dp1 dp2 dp4 dp5 |

c12 | c4 c9 c10 c12 c13 dp6 dp2 dp3 dp5 |

c13 | c5 c10 c11 c13 c14 dp3 dp4 dp6 dp7 |

c14 | c6 c7 c8 c9 c10 c12 c13 dp0 dp1 dp2 dp3 dp5 dp7 |

3.3 性能對比

用VHDL語言對兩種CRC檢驗碼生成方法實現編碼后,利用Model Technology公司的仿真軟件ModelSim SE PLUS 5.6a進行了功能仿真以驗證原理及編碼的正確性。又利用Exemplar Logic公司的綜合工具LeonardoSpectrum對兩種代碼分別進行了綜合,綜合過程中FPGA芯片選取Xinlinx公司的 2s200pq208,速度等級為5級,優化采取自動優化方式,結果如表2所示:

表2 串行和并行CRC編碼性能對比

Area (LUTs) | Delay (ns) | DFFs | Clock (MHz) | |

并行方式 | 35 | 8 | 15 | 119.6 |

串行方式 | 8 | 6 | 15 | 160.9 |

由上表可以計算出,兩種實現方式的速度比為119.6*k/160.9=119.6*8/160.9=5.95,消耗硬件資源比為4.375,時間延遲比為1.33,因而二者性能有很大的差異。

4 結論

由以上討論可以看出:采用串行實現方法、原理和電路結構簡單,消耗硬件資源少,可以工作在較高的時鐘頻率下;采用并行實現方法、原理和實現電路復雜,消耗硬件資源多,工作頻率雖然低于串行方式,但生成CRC檢驗碼的速度(指效率)大大高于串行方式。因而,串行實現方法適合于硬件資源緊缺,檢驗碼生成速度要求不高的場合;而并行實現方法適用于硬件資源豐富,檢驗碼生成速度要求較高的場合。

在實際設計中,采用哪一種CRC檢驗方式,還需要考慮收發幀的需填充位流的結構。為了滿足CAN協議的規定要求(即需檢驗幀起始位,仲裁場、控制場和數據場(若存在的話)組成的未經填充的位流,位流總長度為整數字節多一位),發送支路采用串行方式,可完全按照協議要求生成CRC檢驗碼,接收支路由于多了 15位CRC檢驗碼(外加幀起始位恰好為2個字節),可采用8位并行方式實現CRC檢驗。

參考文獻:

1BOSCH CAN Specification version 2.0

2賈麗媛,戴光明. ATM協議處理中CRC的并行實現. 湖南城市學院學報,(自然科學版)

第13卷,第4期 2004年12月:68~69

3 侯伯亨, 顧新 .VHDL硬件描述語言與數字邏輯電路設計. 西安電子科技大學出版社

評論