OFDM系統中DAGC的應用研究及FPGA實現

2 數據仿真及分析

針對上面所舉例子,用Matlab產生一個長度為1 024的零均值高斯分布復隨機序列,序列方差σ2=2k∈[25,215],k∈[5,15]。定義SNR如式(5),其中Wfloat,Wfix分別是采用浮點、定點FFT算法的平均輸出功率。本文引用地址:http://www.104case.com/article/158081.htm

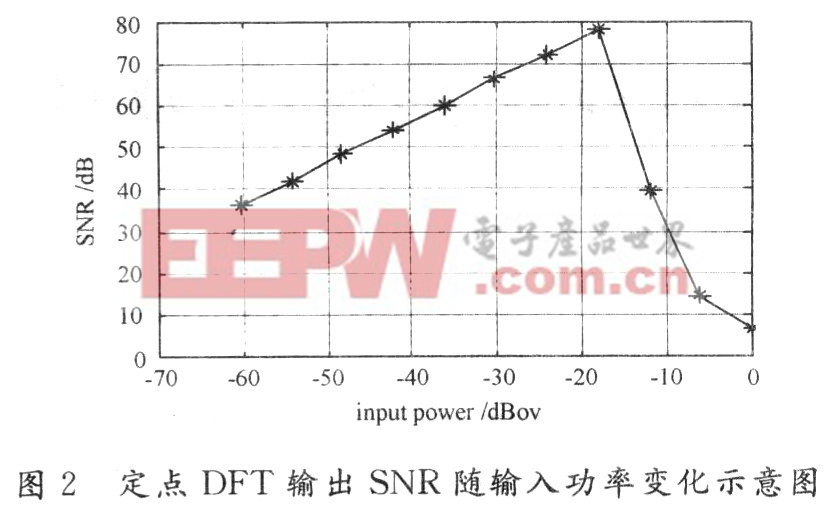

Matlab仿真結果如圖2所示,其中橫坐標為20logl0(σ2/215)。可見,當輸入信號平均功率較小時,量化誤差和舍入誤差隨功率增加而下降,但平均功率上升到一定值后,產生的定點溢出誤差增加使得SNR急劇下降。

針對較大的OFDM符號功率動態范圍,本文采用DAGC技術來調整DFT輸入信號功率,使其處在一個較平穩的范圍內,以此提高DFT運算的輸出SNR,同時減輕本身就具有較大運算量的DFT模塊的負擔。根據仿真結果,結合式(4),選擇DFT輸入平均功率為(210)2時最佳。

3 FPGA實現及分析

由于用FPGA實現乘除法會消耗大量資源,一般采用左右移位來代替。因此,為了簡化FPGA實現難度,本文僅將輸入序列的功率從區間[(2i-1)2,(2i)2]調整到[(29)2,(210)2],其中i為非負整數且i∈[6,15]。

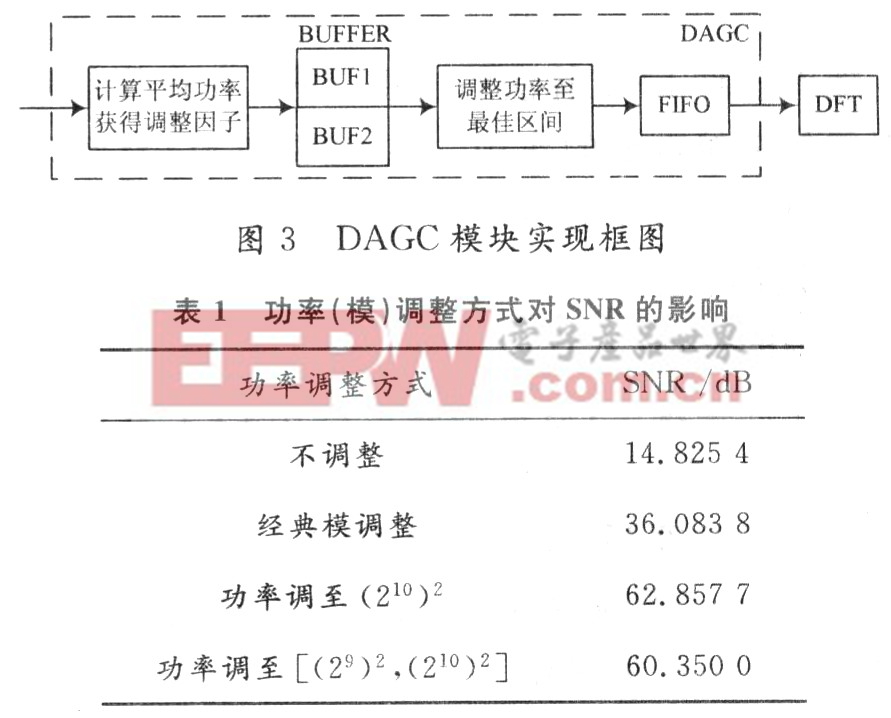

DFT模塊選用Altera公司的IPCORE,總體框圖如圖3所示,其中BUFl,BUF2均可存儲1 024點,用于流水處理。該實現方式通過兩個二級模塊以及中間緩存實現,由于存儲功率的寄存器位寬很大,實現時不使用比較器。流水處理1 024點所需要的平均時間la―tency僅為1 029個時鐘周期,即經過1 024個時鐘周期得到1 024個點后,平均僅需要5個時鐘周期得到功率調整因子。本模塊綜合后的最高頻率fmax=220 MHz。以輸入序列平均功率為2×(214)2為例,功率調整方式對SNR影響如表1所示,其中第三種方式僅由Matlab仿真得到。可見,采用調整到區間[(29)2,(210)2]時的SNR較高且易于用FPGA實現。

4 結 語

本文主要針對OFDM系統中定點化DFT的溢出誤差,分析了DFT輸入信號功率對其輸出信噪比的影響,并以高斯零均值輸入信號為例,采用DAGC與DFT模塊級聯的方式進行了Matlab仿真和FPGA實現,證明了其可行性。該方法以很小的時延、較少的資源以及較高的精度為優勢,有效地增大了定點化DFT正常工作的動態范圍,同時為后級恢復原信號提供了可靠保障,完全滿足0FDM系統基帶解調的要求。

評論