FPGA在多串口讀數系統中的應用

摘要:主要討論了FPGA在多單片機串行讀數系統中的應用,在該系統中單片機通過異步串行通信讀取外部設備中的數據,經FPGA緩沖后再送到USB單片機,最終上傳到計算機。文中重點介紹了利用FPGA內部雙口RAM構建的FIFO在該系統中的具體應用以及FPGA如何協調各單片機的工作。

關鍵詞:FPGA;RAM;FIF0

O 引言

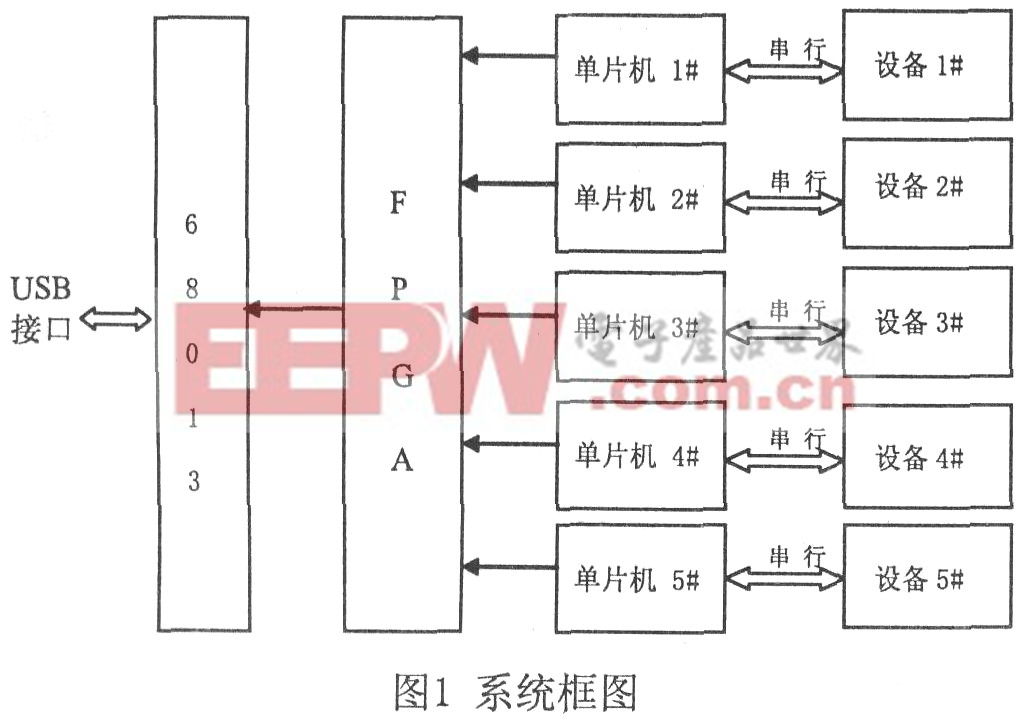

本文所設計的讀數系統主要為解決上傳數據慢的問題,具體的背景如下:目前已設計一小型彈載記錄器,采用單片機+FLASH的結構,FLASH容量為lGB,為了最大限度地減少記錄器的外部接口數據線的數量,采用異步串行通信方式上報數據。單片機選用了Silabs公司混成集成芯片C8051F060,該單片機UARTl最高波特率可以達到系統時鐘的一半,也即如果晶體振蕩器采用14MHz,那么波特率理論值可以達到7Mbps,有效數據傳輸速率可達700kbps,但由于記錄器需要從FLASH讀取數據,而每讀出一頁的數據需要等待約20us的時間,所以上傳數據為非連續性的傳輸,經實際測試發現,波特率為7Mbps時實際的數據上傳速率僅為300kbps左右,如果上傳1GB的數據就需要至少56分鐘的時間,如果需要上傳數套記錄器數據的時候,就顯得尤為浪費時間。為了解決這個問題,本文設計了一個讀數系統,該系統通過增加每次上傳的記錄器的數量來提高讀數系統的資源利用率,以5套記錄器同時上傳來計算,56分鐘內可以上傳5GB的數據,平均每套的上傳時問僅為12分鐘,提高了數據上傳效率。系統框圖見圖l。

其中USB接口控制器選用CYPRESS公司的CY7C68013A,該芯片是Cypress公司推出的新一代高速EZ―USB FX2系列芯片;單片機部分選用C8051F060芯片;主控FPGA選用XILINX公司SPARTAN―IIE系列芯片XC2S100E一PQ208。

FPGA作為主控制中心,主要負責接收68013發送的狀態指令,并將狀態下發到各單片機及相應的外部設備,五個單片機分別負責通過串口接收外部設備的串行數據,并將其并行寫入FPGA,68013除了從FPGA中讀取數據外,還需要將計算機下發的控制命令發送到FPGA。

1 FPGA內部FIF0設計

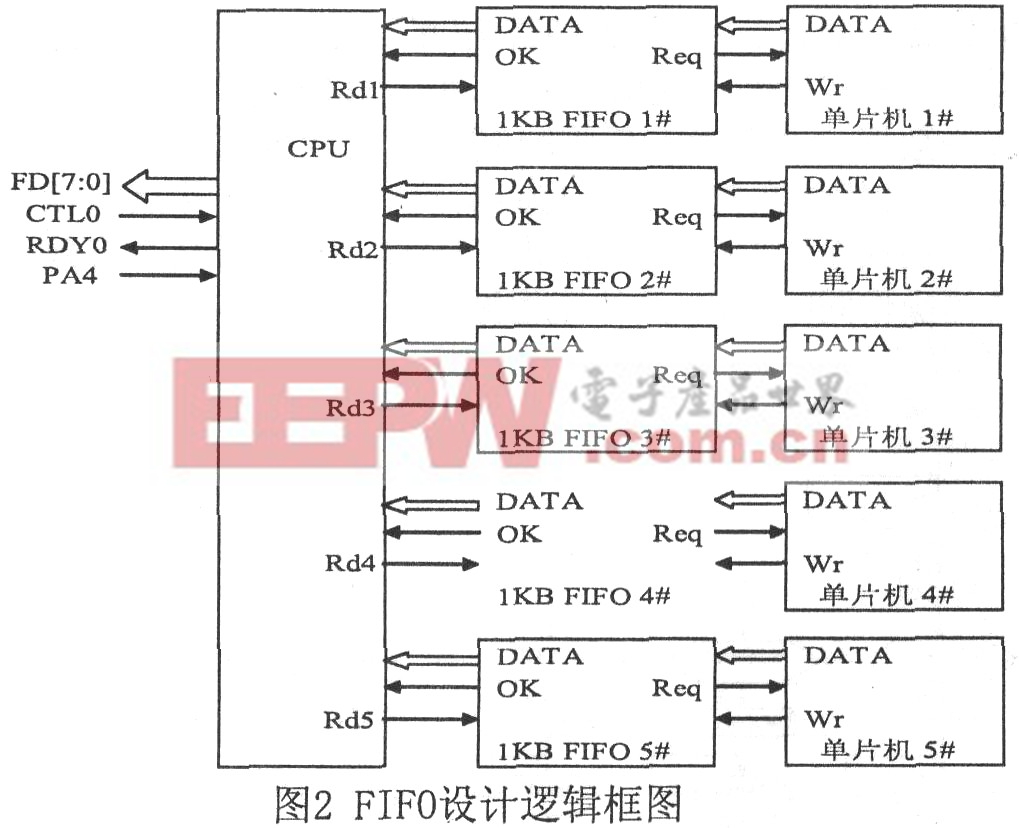

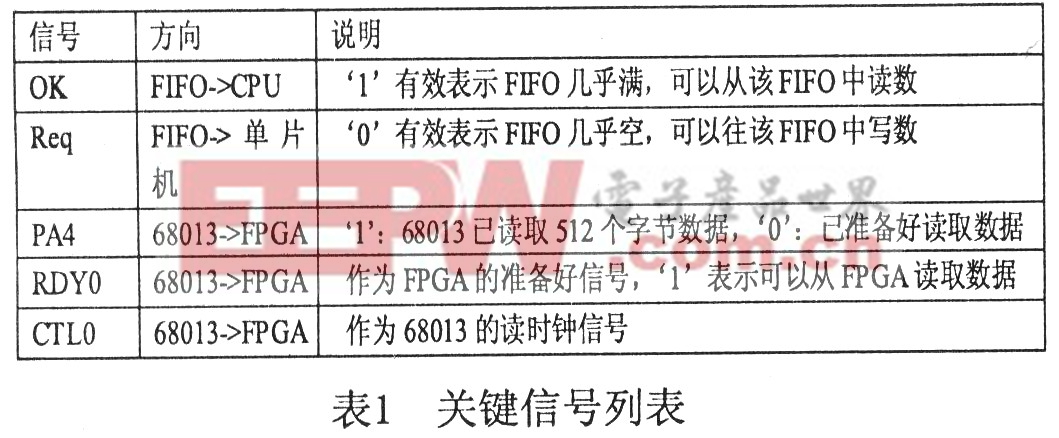

由于本項目所用FPGA芯片內部RAM共有40Kbit,所以可構成1KB×5的FIF0結構,即可構成5個深度分別為1KB的FIFO,分別作為5個單片機上傳時的數據緩沖,具體邏輯框圖見圖2。CPU模塊主要負責五個FIF0之間的切換,5個FIFO采用相同的結構,限于篇幅,本文不詳細介紹FIF0的具體設計,只給出5個FIF0與CPU模塊之間的邏輯關系。5個FIFO分別給出兩個狀態信號,一個是OK,該信號表示FIFO已經準備好數據,可以進行讀取操作,另一個信號為Req,該信號通知單片機該FIFO已經幾乎空,可以向該FIF0寫入數據,其中幾個關鍵信號的具體用途如下表l所示:

2 FIF0切換

GPIF接口是EZ―USB FX2系列單片機提供的一個可由用戶編程的接口,具有高速、靈活等特點,可方便地實現與各種外設之間的無縫連接。GPIF的核心是一個可編程的狀態機,通過對其進行編程可以實現多種協議,功能非常強大。

本設計中68013與FPGA之間的接口即采用GPIF模式,基本的運行模式為:68013每啟動一次GPIF讀波形,便從FPGA中讀取512個字節的數據,然后FPGA自動切換FIFO號。在程序設計時可以在GPIF中斷函數中設置一個標志,這樣CPU模塊在檢測到這個標志后表明對該FIF0的操作已完成,應該切換FIF0了,該標志信號使用PA4引腳來發出,具體說明見見表1。

5個FIFO的具體操作如下:系統上電后先復位各FIFO,并使各FIFO處于關閉狀態,然后判斷是否為讀狀態,如果不是則循環判斷,如果為讀狀態,則使能各FIFO;由于默認操作在FIF0l,所以判斷FIF01的0K信號是有效,如果有效,則判斷PA4引腳是否為‘0’,如果為‘0’則置RDYO為l,68013判斷到此信號后啟動一次GPIF波形讀取512字節的數據,并在讀完后將PA4置1,表示數據已經讀取完畢,CPU模塊在判斷到PA4為1后將RDYO置O,然后將操作對象切換至FIF02,接著判斷FIF02的OK信號是否有效,具體操作同FIF01,具體流程見圖3。

注意:為了保證數據讀取時的暢通無阻,在判斷四個FIF0的OK信號時,應該采取輪循的判斷方式,即當FIF01 的OK信號無效時應該轉去判斷FIF02的0K信號,而不能死等FIF01的0K信號有效,這樣可以有效防止因某個單片機或某個外部設備的故障而出現的讀數停滯現象。

3 結束語

經過長時間的工作表明,該讀數系統能穩定地進行數據的上傳,滿足實際需要。

評論