基于CAN核的四冗余通信板設計與仿真

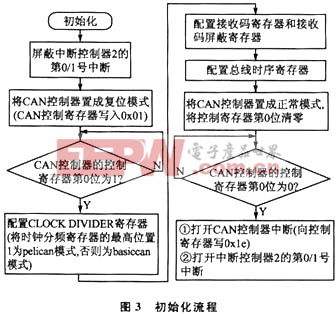

通信板初始化流程如圖3所示。

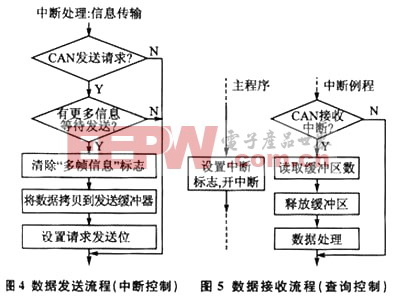

數據發送流程如圖4所示,數據接收流程如圖5所示。

4系統的仿真

采用Modelsim進行仿真。

系統的測試平臺(TestBench),例化了模塊can4core和1個CAN核cantop,并仿真它們之間的通信。

本仿真完全按照CAN核正常工作過程進行,仿真過程如下:

①初始化設置。首先進行時間寄存器的設置和數據格式的設置。通過平臺對本系統設計模塊和CAN核進行設置。

②同步測試。包括硬同步測試和重新同步測試。一個硬同步后,內部的位時間以同步段重新開始。硬同步使引起硬同步的跳變沿位于重新開始的位時間同步段之內。

③空FIFO測試(test_empty_fifo_ext)。該測試通過接收2個數據幀,然后讀取接收緩沖器,接著清空緩沖器,再讀取緩沖器,反復清空和讀取,看FIFO中的數據是否被完全清除。

④滿FIFO測試(test_full_fifo_ext)。首先清空寄存器,然后通過不斷地接收數據幀來填滿FIFO并讀取信息,檢測是否能正常工作。

⑤總線空閑測試(bus-off-test)。通過不斷發送數據來使總線處于忙狀態,致使總線產生錯誤,測試中斷寄存器是否能檢測到錯誤,以及錯誤清除后CAN核能否繼續正常工作。

⑥Basic CAN模式發送幀檢測。測試CAN核能否正常發送幀。

⑦寄存器測試。通過不停地讀寫寄存器,檢測CAN核寄存器是否正常工作。

⑧總線上數據的傳輸。仿真過程中重要的一點就是總線上是否能夠正常傳輸數據信息。

經過仿真可以看到該CAN通信板突破了SJA1000在速度方面的限制,傳輸速度可達2 MHz,有效傳輸速率得到了大幅提高,工作性能良好。

結語

本文設計的CAN總線通信板完成了PC/104與CAN總線的通信轉換,改變了傳統的應用CAN控制器加外部控制器的設計方法,在設計CAN核的基礎上,將通信板中所有數字信號處理部分都放在FPGA內部來實現,使通信速度得到很大提高。無論是在傳輸速率還是在抗干擾、抗震性等方面,CAN核應用的綜合性能都得到了很大的提高。

評論