利用串行RapidIO實現FPGA協處理

本文引用地址:http://www.104case.com/article/157638.htm

傳輸層――為在不同端點設備之間傳送分組提供路由信息 交換設備以基于器件的路由方式工作于傳輸層

交換設備以基于器件的路由方式工作于傳輸層

邏輯層――定義總體的協議和分組格式 每個分組最多包含256字節的載荷

每個分組最多包含256字節的載荷 事務通過Load、Store或DMA操作來訪問大小為34/50/66比特的地址空間

事務通過Load、Store或DMA操作來訪問大小為34/50/66比特的地址空間

SRIO有多種優點 一個運行于3.125 Gbps的4通道SRIO鏈路能在完全保持數據完整性的前提下提供10 Gbps的流量

一個運行于3.125 Gbps的4通道SRIO鏈路能在完全保持數據完整性的前提下提供10 Gbps的流量 SRIO與微處理器總線類似,它在硬件中完成存儲器和器件尋址以及分組處理

SRIO與微處理器總線類似,它在硬件中完成存儲器和器件尋址以及分組處理 這不但大大降低了用于I/O處理的開銷,減小了延遲,也增大了其相對于其他總線接口的系統帶寬

這不但大大降低了用于I/O處理的開銷,減小了延遲,也增大了其相對于其他總線接口的系統帶寬 但與大多數其他總線接口不同的是,SRIO接口的引腳數很少,而且其基于高速串行鏈路的可調整帶寬可在1.25 - 3.125 Gbps范圍內調整

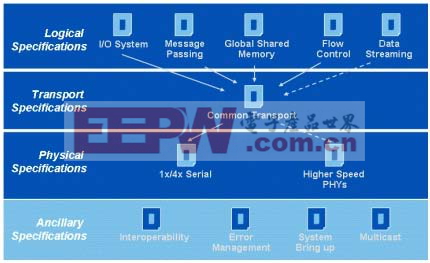

但與大多數其他總線接口不同的是,SRIO接口的引腳數很少,而且其基于高速串行鏈路的可調整帶寬可在1.25 - 3.125 Gbps范圍內調整 圖4為SRIO規范的圖解

圖4為SRIO規范的圖解

圖4:SRIO規范

平臺中的運算資源

有了可配置的處理資源,開發人員就可以用硬件實現他們的應用,例如數據壓縮和加密算法 甚至過去只在軟件中實現的整套防火墻和保密應用,如今都可以在硬件上實現

甚至過去只在軟件中實現的整套防火墻和保密應用,如今都可以在硬件上實現 但這樣做需要具備共享帶寬和強大處理能力的大型并行生態系統,也就是說,要求利用CPU、NPU、FPGA和/或ASIC進行共享式或分布式處理

但這樣做需要具備共享帶寬和強大處理能力的大型并行生態系統,也就是說,要求利用CPU、NPU、FPGA和/或ASIC進行共享式或分布式處理 構建此類系統時,對運算資源的一些要求包括:

構建此類系統時,對運算資源的一些要求包括:

1. 支持復雜拓撲的分布式處理能力;

2. 高度可靠的直接對等通信能力;

3. 多個異構操作系統;

4. 通過多個異構操作系統支持通信數據層;

5. 具有廣泛生態系統支持的模塊化和可擴展平臺

SRIO協議規范和架構支持嵌入式和無線基礎設施領域中運算設備的不同要求 有了SRIO,就可以實現系統結構的獨立性,部署達到運營商級可靠度、具備高級流量管理功能,并具有高性能和高吞吐量的可擴展系統

有了SRIO,就可以實現系統結構的獨立性,部署達到運營商級可靠度、具備高級流量管理功能,并具有高性能和高吞吐量的可擴展系統 此外,廣泛的供應商生態系統也更方便設計師采用現貨元件構造SRIO系統

此外,廣泛的供應商生態系統也更方便設計師采用現貨元件構造SRIO系統 SRIO是一種基于分組的協議,它支持:

SRIO是一種基于分組的協議,它支持:

1. 采用分組操作(包括讀、寫和消息傳遞)實現數據搬移;

2. I/O非一致性功能和緩存一致性功能;

3. 通過支持數據流傳送和SAR功能實現高效的互通和協議封裝;

4. 通過支持數百萬條數據流、256種流量類別和有損操作實現一種流量管理架構;

5. 支持多事務請求流(包括配置QoS)的流量控制;

6. 為減少帶寬分配、事務預定和死鎖避免等問題而支持優先級劃分;

7. 通過系統發現、配置和學習實現對標準拓撲(樹型和網格型)和任意拓撲(菊鏈)等多種硬件拓撲方式的支持,包括支持多個主機;

8. 錯誤管理和分類(可恢復、通知和嚴重)

為了在通過邏輯(I/O)和傳輸層IP上的目標接口和源接口收發用戶數據時支持完全兼容的最大載荷操作,Xilinx等廠商根據最新的RapidIO v1.3規范設計了其端點IP解決方案

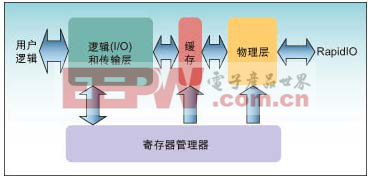

圖5所示是Xilinx的一套完整的SRIO端點IP方案,它包含以下組成部分:

1. LogiCORE RapidIO 邏輯 (I/O)和傳輸層IP;

2. 緩沖層參考設計;

3. LogiCORE串行RapidIO物理層IP;

4. 寄存器管理器參考設計

圖5:Xilinx的 SRIO端點IP架構

IP架構

Xilinx提供了緩沖層參考設計的源代碼,該設計可完成分組的自動排隊和優先級重新劃分 SRIO物理層IP可以實現鏈路訓練和初始化、發現和管理以及錯誤與重試恢復機制

SRIO物理層IP可以實現鏈路訓練和初始化、發現和管理以及錯誤與重試恢復機制 此外,在該物理層IP中還對高速收發器進行了實例化,以便支持線速為1.25Gbps、2.5Gbps和3.125Gbps 的1通道和4通道SRIO總線連接

此外,在該物理層IP中還對高速收發器進行了實例化,以便支持線速為1.25Gbps、2.5Gbps和3.125Gbps 的1通道和4通道SRIO總線連接

該方案中提供的寄存器管理器參考設計允許SRIO主設備對端點設備配置、鏈路狀態、控制和超時機制進行配置和維護 另外,該寄存器管理器還提供了可讓用戶設計探測端點設備狀態的端口

另外,該寄存器管理器還提供了可讓用戶設計探測端點設備狀態的端口

LogiCORE則提供了完整的端點IP 該IP已通過業界領先SRIO器件廠商的測試

該IP已通過業界領先SRIO器件廠商的測試 用戶可通過Xilinx CoreGen GUI工具獲得LogiCORE

用戶可通過Xilinx CoreGen GUI工具獲得LogiCORE CoreGen工具可以幫助用戶配置波特率和端點

CoreGen工具可以幫助用戶配置波特率和端點 LogiCORE支持流量控制、重傳抑制、門鈴和消息傳遞等擴展特性

LogiCORE支持流量控制、重傳抑制、門鈴和消息傳遞等擴展特性 因此,用戶可以創建一套專門針對應用需求優化了的靈活、可調整和定制化的SRIO端點IP

因此,用戶可以創建一套專門針對應用需求優化了的靈活、可調整和定制化的SRIO端點IP

利用Xilinx和其他廠商提供的大多數高性能FPGA中的各種資源,系統設計師就能輕松創建并部署其智能方案,以增強產品在上市時間、可調整性、可擴展性、適應未來發展等各方面的優勢 下面給出了一些采用SRIO和DSP技術的系統設計實例

下面給出了一些采用SRIO和DSP技術的系統設計實例

評論