IR-UWB通信系統高速USB接口的設計與實現

組幀的流程,如圖6所示。usedw表示1 kB FIFO內所存儲的未讀數據的bit數。若usedw≥512則表1 kB FIFO內有512個數據可以被打成一個完整的包。若usedw512表示緩存中的數據不足一幀,這時判斷1 kB FIFO中是否還有數據。若usedw>0,則表示FIFO內還有數據。 Timer_ count是一個特殊的計數器,它表示連續多少個時鐘周期沒有從USB讀取過數據,當從USB讀取數據時,它會被清零。若Time_count=1 024l貝0表示l 024個時鐘周期都沒有從USB讀取過數據,便把1 kB FIFO中剩余的數據補零打包發送出去。

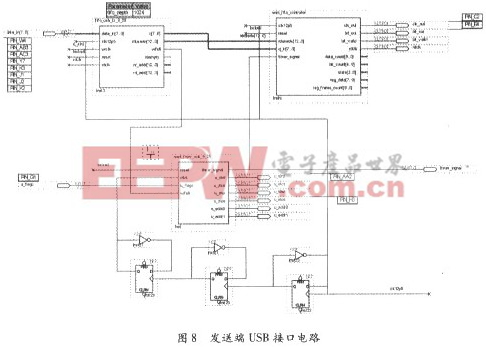

2.4發送端OSB接口電路實現

發送端USB接口電路,如圖8所示。 本文引用地址:http://www.104case.com/article/157580.htm

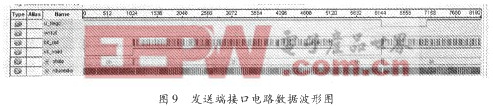

2.5 發送端接口電路數據波形

圖9是利用FPGA開發工具QuartusⅡ6.O提供的虛擬邏輯分析儀邏輯分析測試圖。如圖9所示,u_flagc是USB芯片中FIFO的空滿信號,它表示USB的FIFO中是否有數據,若u_flagc為高電平表示有數據。bit_out是數據進行組幀打包后輸出的比特流,比特流將送入通信系統的基帶部分進行信道編碼。bit_valid為高電平對應bit_out中的有效數據。rdusedw表示FPGA控制電路FIFO中的剩余數據。當FPGA控制電路FIFO中的數據滿512 bit時,控制電路從FIF0中讀取一幀數據。state表示狀態機的狀態轉換,0表示等待狀態,狀態1時發送幀頭數據,狀態2時發送幀長數據,狀態3時發送有效數據。

3 收端計算機與UWB通信系統接口的實現

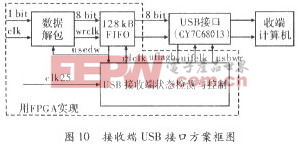

3.1 接收端USB接口方案

如圖10所示,數據解幀模塊通過串行移位寄存器對比特流數據進行初步緩存,同時進行數據幀頭檢測,一旦檢測到幀頭,并且FIFO中有存儲空間,就對緩存的比特流進行解幀處理,將解幀后的數據送入128 kB FIFO,否則一直檢測幀頭。128 kB FIFO模塊用于進行數據緩沖,匹配前后模塊之間速率。USB接收端狀態檢測與控制模塊是用來檢測相應狀態的標志信號,產生同步寫入USB接口FIFO中數據的信號u_ifclk和u_slwr,在u_ifclk的上升沿與u_slwr有效電平期間,將基帶模塊輸出到總線上的數據寫入USB接口芯片中。

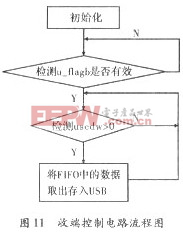

3.2 接收端USB接口芯片控制電路

流程如圖11所示。

評論