FPGA 協(xié)處理的進(jìn)展

盡管FPGA架構(gòu)具有許多出眾的性能,一些性能必須共同發(fā)揮作用,才能提供優(yōu)于CPU協(xié)處理的解決方案。

芯片與算法基礎(chǔ)

大部分雙精度浮點(diǎn)算法的加法與乘法操作比例大約為1:1。在FPGA中,加法運(yùn)算使用邏輯資源,乘法運(yùn)算使用DSP塊,因此FPGA的邏輯資源與DSP塊的比例必須均衡。FPGA的另一個(gè)特點(diǎn)是其可編程功率技術(shù),該技術(shù)可針對(duì)所有邏輯塊、DSP塊與存儲(chǔ)器塊進(jìn)行編程,根據(jù)設(shè)計(jì)的時(shí)序要求將其設(shè)定為高功耗或低功耗模式。

浮點(diǎn)運(yùn)算核已經(jīng)改進(jìn),可運(yùn)行于更高的時(shí)鐘速率,使用更少的DSP塊和更少的邏輯資源。采用浮點(diǎn)編譯器可減少不同浮點(diǎn)運(yùn)算核之間用于連接64位數(shù)據(jù)通路的邏輯資源。

在一次浮點(diǎn)運(yùn)算結(jié)束時(shí),合并對(duì)浮點(diǎn)運(yùn)算進(jìn)行規(guī)格化處理(定點(diǎn)格式轉(zhuǎn)換至浮點(diǎn)格式)的步驟,可以顯著減少對(duì)后續(xù)浮點(diǎn)運(yùn)算輸入的去規(guī)格化處理(浮點(diǎn)格式轉(zhuǎn)換為定點(diǎn)格式)。浮點(diǎn)運(yùn)算的數(shù)學(xué)表達(dá)式的整個(gè)數(shù)據(jù)通路可熔接在一起,這會(huì)最多減少40%的邏輯資源并使時(shí)鐘速率略有提高。

浮點(diǎn)運(yùn)算的正確組合十分重要。如果算法有許多超越運(yùn)算(求指數(shù)、求對(duì)數(shù)等),F(xiàn)PGA可配置所需要的數(shù)目。在GPGPU設(shè)計(jì)中,會(huì)增加一些硬模塊實(shí)現(xiàn)上述函數(shù),但比例比單精度浮點(diǎn)邏輯少得多。使用算法技巧、抽象硬件細(xì)節(jié)及針對(duì)個(gè)別FPGA資源的優(yōu)化都需要函數(shù)庫(kù)。

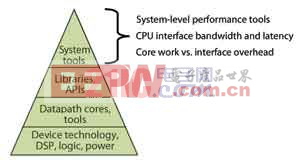

基于芯片、算法與庫(kù)基礎(chǔ),圖2的系統(tǒng)級(jí)解決方案涉及到了工具鏈、模塊/板級(jí)設(shè)計(jì)、CPU接口以及采用合作公司專(zhuān)門(mén)技術(shù)的由CPU至基于FPGA的加速器的數(shù)據(jù)傳輸。

圖2 FPGA加速系統(tǒng)級(jí)解決方案的基礎(chǔ)

使持續(xù)性能接近峰值

對(duì)于可并行化或流水化的任務(wù),相對(duì)于峰值性能而言,F(xiàn)PGA經(jīng)常能夠大大提高持續(xù)性能,并可利用各器件資源。以一個(gè)蒙特卡洛布萊克-斯科爾斯基準(zhǔn)測(cè)試程序?yàn)槔山⒁粭l運(yùn)行頻率為150MHz的等式流水線。

在每個(gè)時(shí)鐘周期,F(xiàn)PGA通過(guò)梅森素?cái)?shù)旋轉(zhuǎn)核產(chǎn)生的隨機(jī)數(shù)被輸入(接入)“定制指令”,每個(gè)時(shí)鐘周期產(chǎn)生一個(gè)結(jié)果。12條“定制指令”與模塊的兩片F(xiàn)PGA匹配,利用雙精度浮點(diǎn)邏輯輸出12×150M=1.8G結(jié)果/秒。通過(guò)額外倍頻,可預(yù)期實(shí)現(xiàn)性能為上述性能的兩倍。

對(duì)比不同架構(gòu)的浮點(diǎn)能力持續(xù)性能與峰值性能十分有趣。表2給出了四種可能解決方案的單精度浮點(diǎn)峰值性能。由于布萊克-斯科爾斯公式需要常規(guī)加法與乘法函數(shù)以外更多的函數(shù)(指數(shù)、平方根等),布萊克-斯科爾斯結(jié)果的總GFLOPS未作統(tǒng)計(jì)。

表3給出了布萊克-斯科爾斯結(jié)果與峰值GFLOPS的比例,作為比較持續(xù)性能與峰值性能的一種相對(duì)衡量方法。相比峰值性能,F(xiàn)PGA達(dá)到了最佳持續(xù)性能。相比另外兩種加速器的單精度邏輯,F(xiàn)PGA的雙精度邏輯具有最優(yōu)原始性能以及最優(yōu)的“性能/瓦”參數(shù)。

對(duì)許多包含并行性或可流水化的算法而言,由于裕量連接帶寬可實(shí)現(xiàn)用戶(hù)自定義的數(shù)據(jù)通路,這樣,邏輯可在一個(gè)時(shí)鐘周期內(nèi)訪問(wèn)存儲(chǔ)器或訪問(wèn)另一個(gè)邏輯塊的結(jié)果,從而使FPGA的持續(xù)性能可接近峰值性能。由于固定架構(gòu)具備預(yù)先確定的用以實(shí)現(xiàn)不同功能的邏輯塊集合,所以可以為FPGA配置支持某種給定算法的最優(yōu)邏輯函數(shù)比例來(lái)實(shí)現(xiàn)器件資源的最佳利用。

評(píng)論