基于FPGA視頻采集中的I2C總線設計與實現

由于SAA7111加電復位之后,各寄存器處于不確定狀態,因此需要采用I2C總線協議由FPGA作為主方對SAA7111的相關寄存器進行設置。從SAA7111的四個模擬輸入端AIll,AI12,AI21,AI22的某一引腳輸入的視頻圖像信號經模擬處理后,一路可通過緩沖器輸出到AOUT端用于監視,另一路經A/D轉換器后則產生數字色度信號和亮度信號。在分別進行亮度信號處理和色度信號處理后,其亮度信號處理結果的一路將送到色度信號處理器進行綜合處理,產生的Y和UV信號經格式化后從VPO(16位)輸出;另一路則進入同步分離器,并經數字PLL產生相應的行和場同步信號HS和VS。同時,PLL將驅動時鐘發生器,以產生HS鎖定的時鐘信號LLC和LLC2,SAA7111的所有功能均是在I2C總線控制下完成的。SA-A7111相應的寄存器初始化值見表1。本文引用地址:http://www.104case.com/article/157385.htm

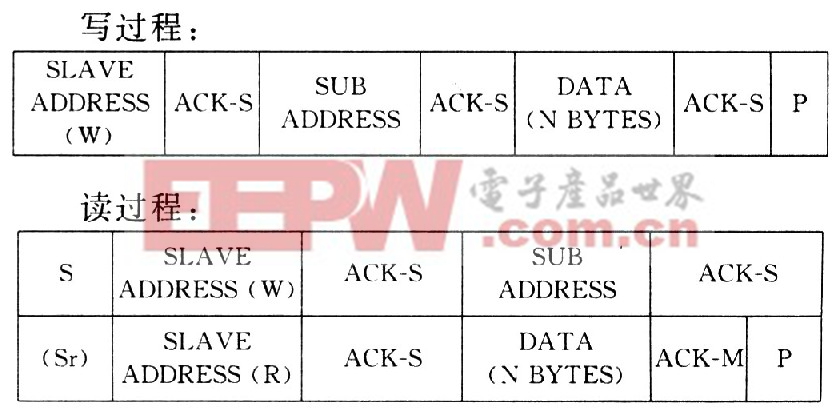

I2C總線控制讀/寫操作過程如表2、表3所示(S:開始,Sr:重開始,P:停止,-S:從設備,-M:主設備,W:寫位,R:讀位):

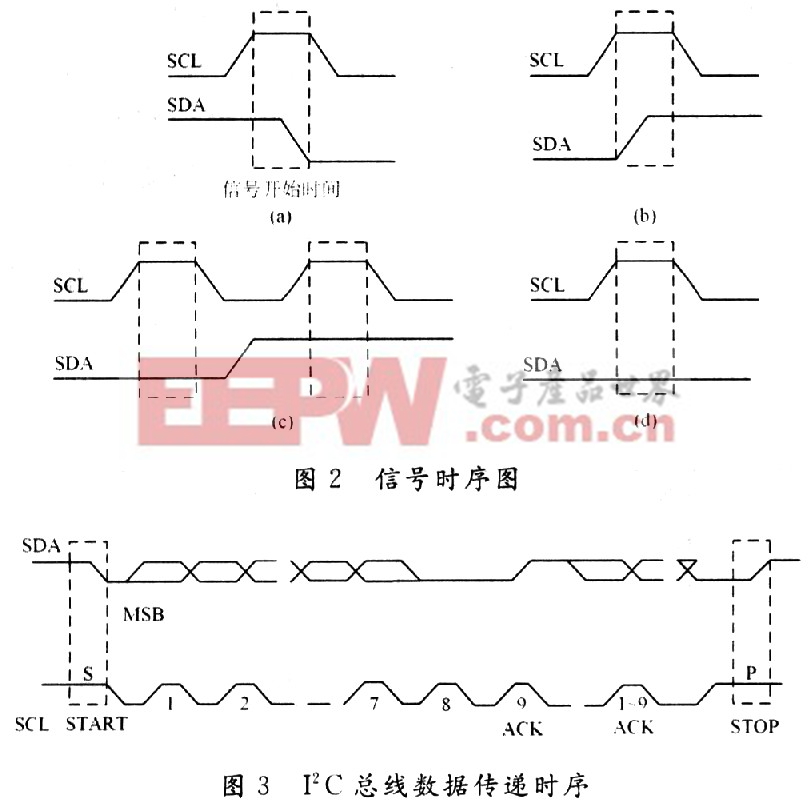

在設計中主要實現以下四種功能:開始條件功能、字節發送功能、應答條件功能和停止條件功能。四種功能信號的時序和數據總線傳遞如圖2、圖3所示。

為了完成上述要求和功能,本文采用VHDL語言編寫邏輯的方法來模擬I2C總線接口時序邏輯,配置數據可以由主機發送,也可以預先存放,同時用VHDL編寫時序邏輯對SAA7111進行初始化配置。根據設計要求,在不同的進程下對串行時鐘線(SCL)和串行數據線(SDA)進行設計。時鐘信號源采用10 MHz的晶振,分頻后作為進程激勵信號,基本能夠滿足SAA7111芯片的數據率要求。但如果在一些更高速的情況下,需要快速通過I2C總線對被控器件進行設置,這里只需將行時鐘線(SCL)和串行數據線(SDA)的頻率進行修改即可,其接口控制如圖4所示。

評論