基于FPGA的高速通信系統研究

2.2 傳輸部分電路設計

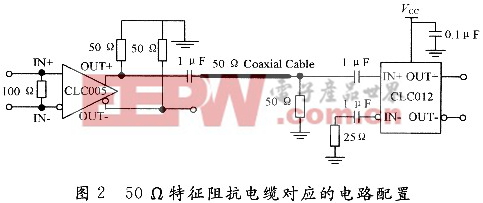

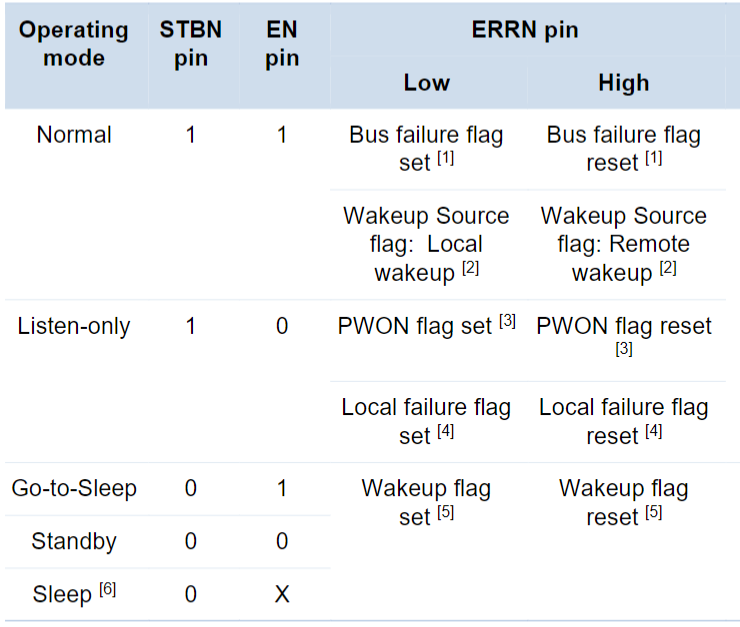

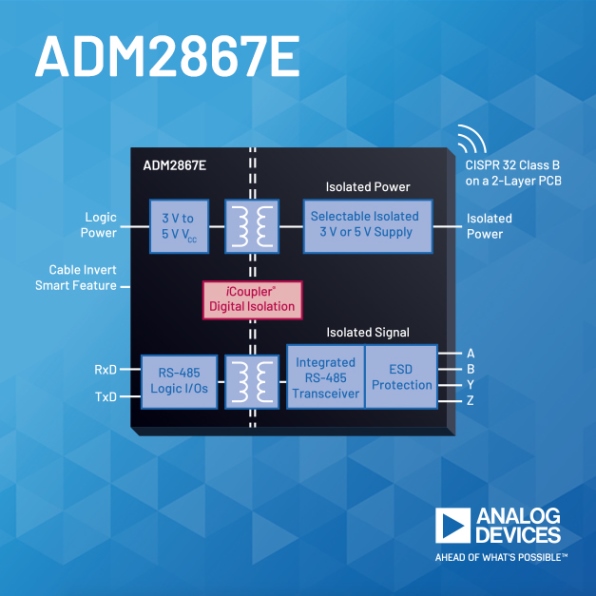

傳輸部分設計包括選擇同軸電纜和設計相應的發送接收電路。本系統選用的同軸電纜型號為SVY-50-3,成本低、性能好。這款電纜的特征阻抗為50 Ω,速率150 MHz時信號傳輸100 m的最大衰減為18.01 dB。它具有良好的屏蔽特性,可以在復雜的電磁環境中正常工作。電纜驅動電路和接收均衡電路分別選用National Semiconductor公司的芯片CLC005和CLC012。CLC005支持LVDS電平輸入,最高傳輸速率達到622 Mb/s,輸出信號峰一峰值從O.7~2 V。CLC012可以自動均衡頻率在50~650 MHz的信號。時鐘恢復器件選用CLC016,它的輸入信號來自CLC-012,輸出時鐘和數據接FPGA,恢復的時鐘在數據上升沿有效。CLC005和CLC012用于特征阻抗為75 Ω的傳輸系統,針對本系50 Ω特征阻抗的同軸電纜,需要改動外圍電阻配置,否則會因為阻抗不匹配引起信號反射,最終導致信號傳輸質量下降。相應的配置方式如圖2所示。本文引用地址:http://www.104case.com/article/157077.htm

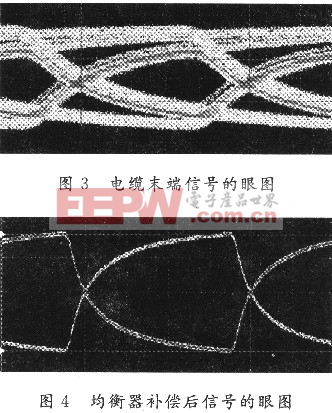

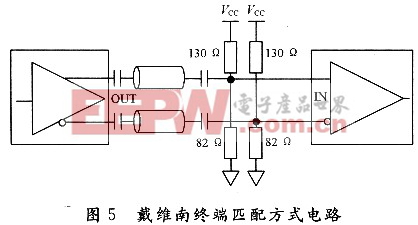

通過測試,此組傳輸器件可以驅動LVDS信號通過SVY-50-3型號電纜傳輸至少200 m。信號經過傳輸后,在電纜末端衰減嚴重,噪聲和抖動也較嚴重。此時信號眼圖如圖3所示,可以看出信號質量差。直接接收此信號,會產生信號電平誤判,而且信號的抖動將導致后級電路無法正常工作。接收均衡器CLC012自動為信號損耗提供補償后,信號上的噪聲和抖動均得到了改善,信號的眼圖如圖4所示。

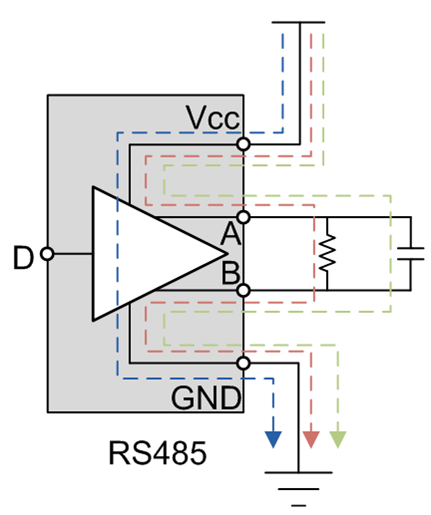

LVDS驅動器由恒流源構成,因此需要做終端匹配。通常情況下在輸入端并聯100 Ω電阻從而滿足互聯系統要求的差分阻抗。在強噪聲環境下,交流耦合連接時可以采用戴維南終端匹配方式提供1.2 V的偏置電壓,同時滿足100 Ω差分阻抗的設計要求。具體方法是將LVDS的+/-端通過130 Ω電阻上拉至VCC,同時下拉82 Ω電阻到地,如圖5所示,電阻精度要求在1%。

評論