Adsp-TS101性能分析及其在雷達信號處理中的應用

Adsp-TS101性能比ADSP21160有顯著提高,且與之兼容,使得以ADSP21160開發的產品升級快速、簡捷。Adsp-TS101是64位處理器,工作在250 MHz時鐘下,可進行32位定點和32位或40位浮點運算,提供最高1500 MFLOPS(Millions of floating-pointoperations per second,每秒執行百萬次浮點操作)的運算能力;內部具有6 M位雙口 SRAM,同時集成了I/O處理器,加上內部總線,消除了I/O瓶頸。此外,Adsp-TS101適宜多處理器結構,內部集成總線仲裁,通過鏈路(1ink)12I和外部(external)口可支持并行處理器,而不需任何附加邏輯電路,每一個處理器可直接讀寫任何一個并行處理器的內存。本文簡要介紹其性能、應用特點及芯片內部的系統結構和功能框圖,給出Adsp-TS101的一種典型應用,并說明DSP的電源供電和功耗的計算方法。

本文引用地址:http://www.104case.com/article/157055.htm1 Adsp-TS101的主要性能

Adsp-TS101的主要性能如下:

采用TigerSHARC結構,具有3條獨立總線用于取指令、取數據、不間斷I/O;

指令周期4 ns,工作時鐘250 MHz;

單指令流多數據流(SIMD)提供兩個運算單元,每個有一個算術邏輯單元、乘法器、移位器、寄存器組,可同時在兩個運算單元上進行同一指令下對不同數據的32位操作;

提供最大1 500 MFLOPS運算能力;

片內6 M位雙口SRAM,允許CPU、Host和DMA的獨立存取;

有14個DMA通道,可進行內存和外存、外設、主處理器、串(serial)口、鏈路(1ink)口之間的數據傳輸;

有2個數據地址發生器(IALU),允許取模和按位取反操作;

片內集成I/0處理器、6 M位雙口 SRAM,具有串行、連接、外部總線和JTAG測試口,支持多處理器結構;

并行總線和多運算單元,使單周期可執行1次算術邏輯運算、1次乘法、1次雙口SRAM的讀或寫,以及1次取指操作,CPU與內存之間可進行每周期4個32位浮點字的傳輸;

簇式多處理器最高可支持8個TigerSHARC Adsp-TS101。

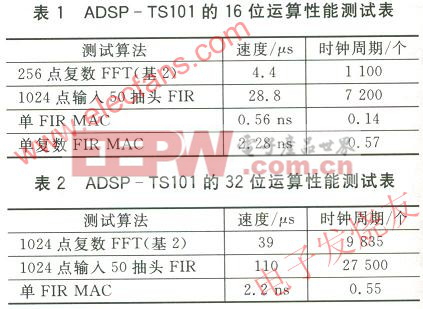

Adsp-TS101性能測試如表1、2所列。

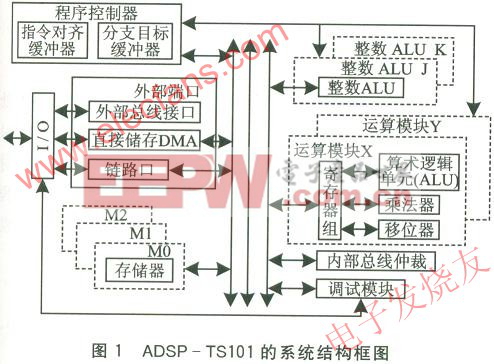

2 Adsp-TS101的系統結構框圖和功能簡介

圖1為ADSP一TSl01的系統結構框圖。由圖可見,Adsp-TS101包括PEX、PEY兩個運算單元,每一個浮點運算有一個算術邏輯單元、乘法器、移位器、32字寄存器組。另外,算術邏輯單元、乘法器、移位器為并行排列,可進行單周期多功能操作,如在同一機器周期中算術邏輯單元和乘法器可同時進行操作。

當數據在存儲器和寄存器之間傳遞時,IALU提供存儲器的地址。每個IALU有一個算術邏輯單元、32字寄存器組。

程序控制器包括指令隊列緩沖器(IAB)和分支目標緩沖器(BTB)。Adsp-TS101既有4個外部中斷IRQ3~O,也有內部中斷。

3條128位總線提供高的寬帶連接。每個總線允許每個周期4條指令或4隊列數據進行傳輸。外部口和其他鏈路口的片上單元也用這些總線訪問存儲器。在每個周期僅能訪問一個存儲器塊,故DMA或外部口傳輸與處理器核在訪問同一塊時必須進行競爭。

評論