基于VHDL的2FSK調制解調器設計

3.2 仿真結果

在MAX+PLUS軟件平臺上進行布局布線后進行波形仿真,其中clk為輸入主時鐘信號;start為起始信號,當start為“1”的時候,開始解調;x為輸入信號,本文中在調制階段的被調制信號,即是調制信號中的輸出信號,y為輸出信號,在正常情況下y就是在調制信號中的輸入信號,在 q=11時,m清零。在q=1O時,根據m的大小,進行對輸出基帶信號y的電平的判斷。在q為其它值時,計數器m計下xx(寄存x信號)的脈沖數。輸出信號y滯后輸入信號×10個clk。仿真結果如圖5所示。

4 2FSK調制解調器整體設計

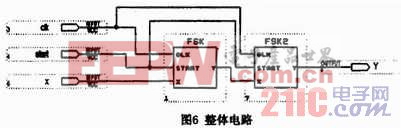

在整體設計過程中,整體電路如圖6所示,其中x為基帶信號,y為經過調制解調后的解調信號。

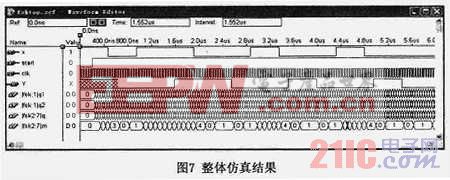

調制解調器設計仿真結果如圖7所示。比較輸入信號x與輸出信號y,完全一樣,只是系統仿真結果有一定的延時。仿真結果表明,系統設計正確。

5 結論

本文基于2FSK的基本原理,進行二進制調制解調器的設計。運用VHDL語言對器件進行功能描述,在MAX+PLUSⅡ軟件平臺上對所描述器件進行時序仿真,最后下載至目標芯片EPM7032LC44-15,分配合理引腳,進行仿真。設計過程中調制階段的基帶信號,經調制仿真得到解調所需的輸入信號。解調階段對來自調制階段得到的信號進行解調,所得解調信號即為原來調制基帶信號,起到了調制解調的作用。整個設計過程采用VHDL語言實現,設計靈活、修改方便,具有良好的可移植性及產品升級的系統性。

本文引用地址:http://www.104case.com/article/156781.htm

數字通信相關文章:數字通信原理

低通濾波器相關文章:低通濾波器原理

分頻器相關文章:分頻器原理 脈沖點火器相關文章:脈沖點火器原理

評論