基于PowerPC的光纖通道接口卡設計

Xilinx公司提供的EDK開發工具是一種專門針對FPGA內部嵌入式處理器的集成開發工具包,主要的軟件設計由EDK中的子工具包SDK完成。用戶可以通過集成在EDK中的XPS來調用各種工具完成嵌入式系統平臺的搭建工作。

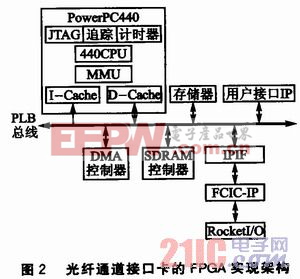

EDK10.1版本較之9.1版本有很大的變化,其中軟核版本升級到7.1,IBM CoreConneet總線標準中的OPB總線被PLB總線代替,還提供了豐富的外圍IP可供選擇。光纖通道接口卡的FPGA實現架構如圖2所示。

(1)PowerPC處理器和高速存儲器通過PLB高速總線互聯在一起構成嵌入式操作系統和軟件系統的運行平臺。

(2)用戶接口IP提供一個方便的接口,供外部設備操控接口卡芯片,亦可對該芯片的工作狀態進行動態監控。

(3)采用FPGA芯片內部集成的可編程高速串行收發器RoeketI/O來負責數據的發送和接收。

(4)在數據發送端,硬件通過DMA方式讀取與序列和交換管理有關的隊列,然后根據隊列中的信息,確定每個幀頭的內容,再通過DMA方式讀取管理內存中的數據并組裝成幀發送出去;在數據接收端,硬件接收到幀后,通過DMA方式寫到內存中,軟件負責將幀重組為序列,再將序列重組成交換。

3 IPIF模塊

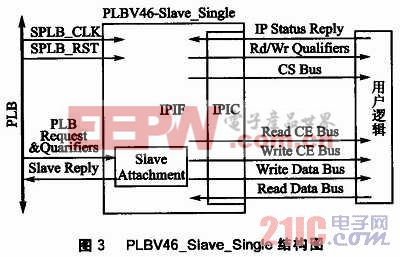

由于PLB總線接口協議非常復雜,為了讓用戶可以更便捷地實現總線與用戶IP的交互,Xilinx公司提供了在用戶IP核和PLB v4.6總線標準之間的一個雙向的PLBV46_Slave_Single接口協議模塊IPIF,如圖3所示。

其中的Slave Attachment結構提供了Slave運行的基礎功能,它在PLB總線和IPIC之間執行協議和時序的轉換。用戶IP的用戶邏輯接口需按照IPIC接口標準來設計,才能通過IPIF成功掛接到PLB總線上。

利用集成在EDK的XPS工具中Create/Import Peripheral Wizard(添加外設向導工具),以對話框的形式可以很便捷地配置IPIF模塊,以Master/Slave的方式將用戶自定制IP核掛接到PLB總線上,通過ISE1O.1環境綜合驗證模塊的正確性。然后再利用此工具,將經過驗證正確的IP核導入EDK環境下,這樣就成功建立了一個IP核的通用模板。最后再在相應的.VHD文件中添加用戶功能代碼,即可完成基于PLB總線接口的用戶自定制IP核的添加。

結語

本文設計的光纖通道接口卡芯片采用Xilinx公司推出的新一代嵌入式硬核PowerPCA40,利用EDK開發工具,在Virtex5系列FPGA開發平臺上實現了接口卡芯片的基本功能,支持點對點拓撲結構和仲裁環拓撲結構,為用戶自定制IP核的開發應用提供了一定的參考。

本文引用地址:http://www.104case.com/article/156776.htm

評論