基于NIOS II的多串口數據通信的實現

圖4中SET_EN用于設置個串口的輸入模式(是否乒乓輸入及乒乓輸入時緩存的大小)和串口使能等操作,輸入控制寄存器的默認值在系統初始化時由DSP寫入。

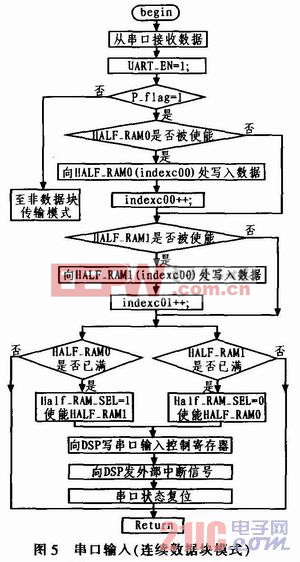

當數據輸入時,NIOS II CPU檢測到來自串口的中斷請求,進入對應的中斷響應程序。首先對數據傳輸模式進行判斷,P_flag默認值為0,表示非數據塊輸入模式。該模式下輸入的數據有特定的結尾標志符組合,一旦檢測到結束標志則發送已緩存的數據并完成狀態清零以便下次接收;P_flag為1則為連續數據塊輸入,當Half_BAM0或Half_RAM1其中一塊寫滿時即向DSP發出中斷信號,DSP即進入中斷服務程序讀取數據。程序流程圖如圖5所示。

3 結束語

采用Altera FPGA芯片上的NIOS II CPU控制串口的優點是充分使用硬件資源,可以減輕DSP芯片的計算量。測試表明,NIOS II CPU工作頻率為20.46 MHz,串口波特率設置為115 200,數據位為8 bit,各串口可以同時正常輸入輸出。多串口可以同時輸入輸出數據,由指令可以靈活配置傳輸模式,以適應不同數據傳輸類型的需求。

本文解決了單串口傳輸不能滿足GPS高精度接收機對多種數據同時輸入輸出的要求,實現了GPS定位結果、RTK差分數據與外界的實時交換以及用戶控制命令的輸入。本方案的優點是通過增加各串口的輸入/輸出控制寄存器,使DSP芯片可以僅以兩個GPIO資源實現原本需要3個串口輸入/輸出功能相對應的6個中斷操作;采用NIOS II CPU進行多串口控制可以減少硬件調試時間,節約FPGA片內資源。不足之處是未實現串口波特率、數據位等實時配置。

評論