用LatticeXP FPGA 橋接吉比特媒體獨立接口

吉比特媒體獨立接口是一種以太網接口,簡稱GMII(Gigabit Media Independent Interface)。簡化的吉比特媒體獨立接口稱為RGMII(Reduced Gigabit Media Independent Interface)。采用RGMII的目的是降低電路成本,使實現這種接口的器件的引腳數從22個減少到12個。本文主要介紹用萊迪思半導體公司的LatticeXP FPGA實現RGMII至GMII的雙向橋接功能,能在RGMII和GMII之間雙向傳送數據。

LatticeXP將低成本的FPGA結構和非易失、可無限重構的ispXP(eXpanded Programmability:拓展了的可編程性)技術結合起來,能實現瞬時上電和單芯片應用,還具備出色的安全性。LatticeXP提供了一種用于替代基于SRAM的FPGA和與之相關的引導存儲器的低成本選擇方案。由于新的LatticeXP器件采用了130納米閃存硅處理工藝、優化的器件結構和專有的電路設計,其芯片尺寸比萊迪思過去的非易失FPGA降低了80%以上。

LatticeXP器件采用ispXP技術,該技術將SRAM和非易失的閃存結合起來,使FPGA同時具備了非易失性和無限可重構性。非易失的可無限重構FPGA,連同其瞬時上電的操作性能和安全的單芯片解決方案,有了這樣一種FPGA,用戶就可以同時獲得SRAM的無限可重構性和非易失性的眾多優點。

LatticeXP FPGA器件結構的主要特點如下:

●以易于綜合的工業標準四輸入查找表(LUT)邏輯塊為基礎結構。

●只有25%的邏輯塊包含分布式內存,這一優化既滿足了大多數用戶對少量分布式內存的需求,又降低了成本。

●由于器件擁有sysCLOCK鎖相環(PLL)和內嵌模塊RAM(EBR),用戶可將這些功能集成在FPGA中,無需采用離散元器件,進一步降低了成本。

●先進的sysI/O緩沖器支持LVCMOS、LVDS、LVTTL、PCI以及SSTL和HSTL等標準,便于輕松高效地連接業界最流行的總線標準。萊迪思精心選擇了這些標準,以最大程度地拓展應用范圍并減小芯片面積。

●LatticeXP器件中有專門用來簡化DDR存儲器接口的電路,為這類FPGA提供高性能、一體化、信號完整性和易于設計的特性。

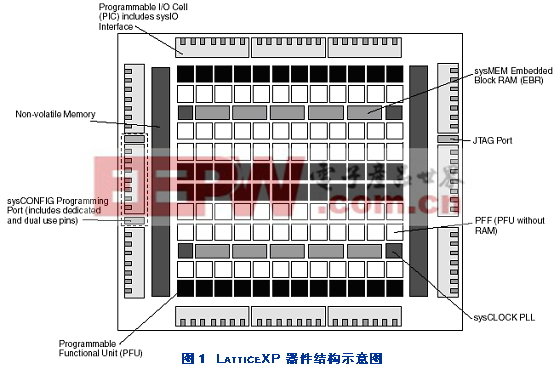

LatticeXP器件結構如圖1所示,器件的中間是邏輯塊陣列,器件的四周是可編程I/O單元(Program I/O Cell,簡稱PIC)。在邏輯塊的行之間分布著嵌入式RAM塊(sysMEM Embedded Block RAM,簡稱EBR)。

PFU陣列的左邊和右邊,有非易失存儲器塊。在配置模式,通過IEEE 1149.1口或sysCONFIG外部口對非易失存儲器塊編程。上電時,配置數據從非易失存儲器塊傳送至配置SRAM。采樣這種技術,就不再需要昂貴的外部配置存儲器,設計沒有未經許可的讀回風險。數據從配置數據經寬總線從非易失存儲器塊傳送至配置SRAM,這個過程只有數毫秒時間,提供了能容易地與許多應用接口的瞬時上電能力。

器件中有兩種邏輯塊:可編程功能單元(Programmable Function Unit,簡稱PFU);無RAM的可編程功能單元(Programmable Function Unit without RAM,簡稱PFF)。PFU包含用于邏輯、算法、RAM/ROM和寄存器的積木塊。PFF包含用于邏輯、算法、ROM的積木塊。優化的PFU和PFF能夠靈活、有效地實現復雜設計。器件中每行為一種類型的積木塊,每三行PFF間隔就有一行PFU。

每個PIC塊含有兩個具有sysIO接口的PIO對。器件左邊和右邊的PIO對可配置成LVDS發送、接收對,sysMEM EBR是大的專用快速存儲器塊,可用于配置成RAM或ROM。PFU、PFF、PIC和EBR塊以行和列的形式分布呈二維網格狀,如圖1所示。這些塊與水平的和垂直的布線資源相連。軟件的布局、布線功能會自動地分配這些布線資源。系統時鐘鎖相環(PLL)在含有系統存儲器塊行的末端,這些PLL具有倍頻、分頻和相移功能,用于管理時鐘的相位關系。每個LatticeXP器件提供多達4個PLL。該系列中每個器件都帶有內部邏輯分析儀(ispTRACY)的JTAG口。系統配置端口允許串行或者并行器件配置。LatticeXP器件能工作于3.3V、2.5V、1.8V和1.2V的電壓,易于集成至整個系統。

這個設計的主要功能為:

● GMII至RGMII的數據橋接

● RGMII至GMII的數據橋接

評論