基于CPRI協議的光纖通訊設計與實現

2.2 時鐘方案

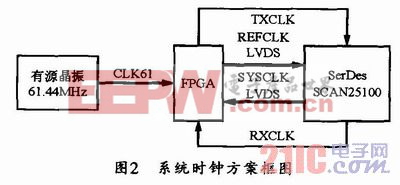

采用輸出頻率為61.44MHz的有源晶振為FPGA提供系統基準時鐘(CLK61),系統所需的其他頻率時鐘,均可使用FPGA內置的時鐘管理模塊,對CLK61進行分頻、倍頻及移相而得。SCAN25100有四個時鐘端口,與FPGA相連。系統時鐘方案如圖2所示。本文引用地址:http://www.104case.com/article/156425.htm

SCAN25100芯片內置振蕩器能夠產生一個30.72MHz時鐘SYSCLK輸出,提供給FPGA作參考時鐘。當系統作為REC端時,FPGA需要提供一個30.72MHz時鐘REFCLK,給SCAN25100作為參考時鐘。REFCLK和SYSCLK均使用LVDS差分電平,在FPGA內部使用緩沖器IBUFGDS來將輸入差分時鐘信號轉為單端時鐘,而使用OBUFDS將單端時鐘轉為差分時鐘輸出。

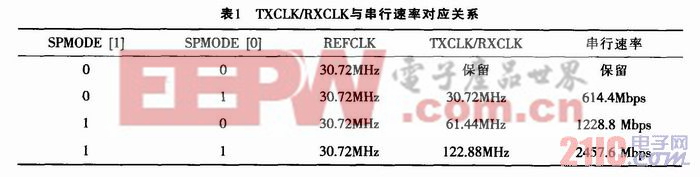

TXCLK為FPGA輸出給SCAN25100,用于采集輸出數據tx_data(9:0)的時鐘。RXCLK為SCAN25100輸出給FPGA,用于采集輸入數據rx_data(9:0)的時鐘。TXCLK和RXCLK配置使用INCMOS18電平,均為雙邊沿采集數據,其時鐘頻率由用戶根據需求配置SCAN25100串行接口(DOUT和RIN)的傳輸速率決定。SPMODE(1:0)的配置值決定傳輸速率,對應關系見表1。

評論