單片機脈沖信號源的CPLD實現方案

由上式可以看出信號源最高輸出頻率取決于系統時鐘頻率,最高頻率為系統時鐘頻率的一半(C1、C2均為1),要提高信號源輸出頻率必須提高系統時鐘頻率,既采用高頻晶振或倍頻電路。占空比取決于C1與C1+C2的比值,輸出頻率為最高頻率時,占空比為50%;同樣最小步進也取決于系統時鐘頻率,提高系統時鐘頻率,就可使步進縮小。

如果要信號源輸出頻率為500 kHz,占空比為0.5的脈沖波,則按式(1)、式(2)可以算出,C1=C2=HB0(16進制數)。將C1、C2通過工控機置入CPLD中。如果C1、C2為小數,則需取整,取整后需按式(3)、式(4)重新計算頻率和占空比,算出的值為實際的頻率與占空比。

2 硬件編程

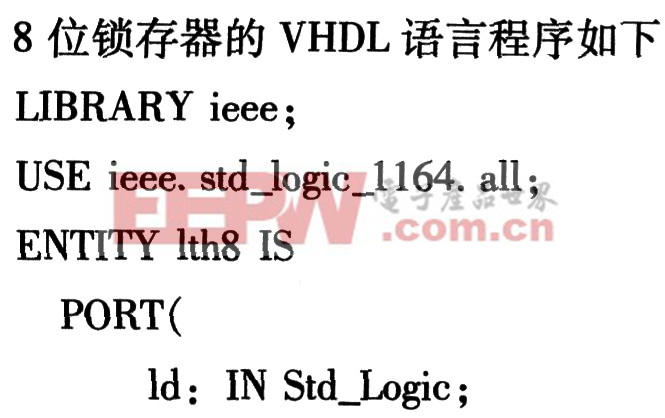

開發軟件采用Max PlusⅡ10.2,編程采用VHlDL硬件描述語言。

編程采用層次結構,整個程序采用頂層模塊和底層模塊。頂層模塊,如圖4所示。底層模塊包括系統包含的各組件。

整個程序編寫完成后進行編譯、仿真,仿真結果,如圖5所示。編譯、仿真通過后都正確,即可通過JTAG接口將程序下載到目標板CPLD中,目標板即可使用。

3 系統控制軟件

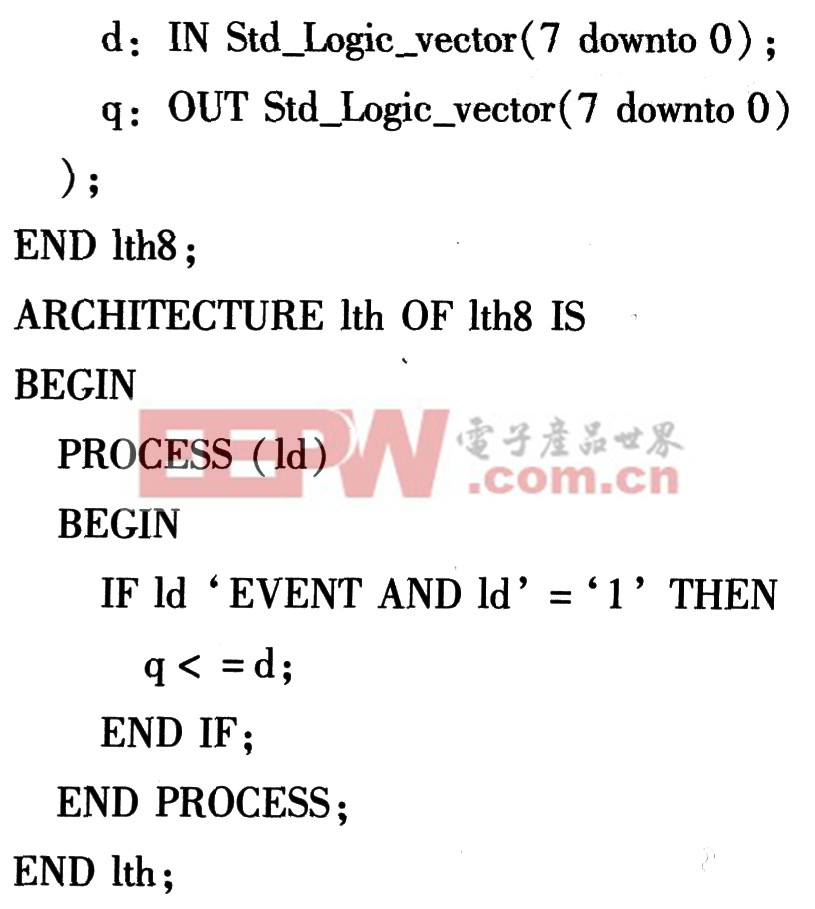

系統控制軟件采用LabWindows/CVI編寫,為了給鎖存器置數,可采用如下程序實現:

4 技術指標

本脈沖信號源輸出脈沖頻率:20~700 kHz,占空比:1%~40%,時鐘采用80 MHz有源晶振。在700 kHz時頻率步進為6 kHz,20 kHz時頻率步進為5 Hz。

由于采用了EPM7128SLC84—10作為脈沖信號源的核心。電路結構簡單,頻率、占空比可任意設置,準確度高。同時操作簡單方便,功能更易擴展。

評論