一種雷達通用信號處理系統的實現與應用

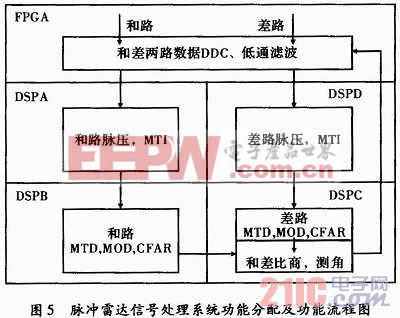

處理流程:FPGA將接收到的和差兩路信號分別進行DDC以及低通濾波,并對結果進行整理,和路信號發送給DSPA,差路信號發送給DSPD。在DSPA和DSPD中分別進行和路以及差路信號的脈壓、MTI,其中MTI可以是根據命令選做的。DSPA將處理完的信號傳送給DSPB,DSPD將處理后的數據傳送給DSPC,在DSPB和DSPC中進行和路以及差路信號的MTD、MOD、CFAR,同時DSPC接收DSPB處理后的信號,在DSPC中進行和差比商測角,最后將整理后的結果輸出到FPGA,由FPGA輸出給雷達的其它模塊,如圖5所示。本文引用地址:http://www.104case.com/article/156265.htm

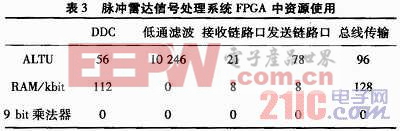

資源使用:在FPGA需要完成的功能為兩路信號的DDC、低通濾波,以及與DSP的數據通信。其中在做DDC時為了便于測試在FPGA內部有Mat-lab產生的兩組數據分別作和差兩路數據的內部源數據。與DSP交互部分無論是總線傳輸還是鏈路口傳輸均與連續波雷達信號處理實現方法一致,在此不再贅述(假設FPGA到DSP傳輸數據為1 024個復數)。則在FPGA中占用的主要資源如表3所示。

在DSPA和DSPD中以乒乓方式接收FPGA的數據完成數據的定浮轉換,脈沖壓縮和MTI。其中脈沖壓縮采用頻域脈壓的方式,然后對脈壓結果作MTI,采用四脈沖對消。在DSPB和DSPC中要完成數據的MTD,MOD,CFAR,最后在DSPC中實現測角,最終將目標數據結果傳輸給FPGA。這些功能的實現與連續波雷達實現這些功能方法相同,在此不再贅述。則在DSP中所占用的資源如表4所示。

2.3 幾個重要模塊的速度

在實時信號處理系統中,系統的速度至關重要,本文所介紹的平臺在各個接口及模塊上均能達到不錯的速率。

(1)FPGA與DSP總線傳輸速率。

在本系統中總線傳輸可以采取流水協議,零等待周期的配置,這樣總線速度可以達到DSP SCLK的速度,在本系統中為50 MHz×64 bit的速率。

(2)FPGA與DSP鏈路口傳輸速率。

在本系統中鏈路口采取四位模式,則鏈路口可以配置成150 MHz,300 MHz,400 MHz,600 MHz。經過測試,FPGA與DSP之間的鏈路口速度可以達到400 MHz×4 bit的完美無錯傳輸。

(3)DSP與DSP鏈路口傳輸速率。

經過測試,DSP與DSP之間的鏈路口速度可以達到600 MHz×4 bit的無錯傳輸。以上幾個速率為數據傳輸十分重要的幾個接口的速度,通過測試數據可知,系統可以達到較高的,完全可以滿足信號實時性的要求。

3 結束語

針對當前FPGA+DSP的信號處理平臺現狀,提出一種通用的硬件結構,該結構不僅將兩種處理器的優點集于一身,兼顧速度和靈活性而且可以應用在不同雷達信號處理系統中,具有很強的通用性。分別介紹了此平臺在連續波雷達以及脈沖雷達中的一種應用,并且這些方法已經成功應用于雷達信號處理機中。除了文中列舉的方法外由于本結構硬件連通的靈活性,本結構可以根據需要應用于各種雷達處理系統中。

評論