基于光纖通道的IEEE1394光信號傳輸系統設計

FPGA內部的工作過程說明如下:IEEE1394數據從16:32解復用器輸出之后,進入IEEE1394數據拆分模塊,產生對應于FC數據幀的SOF、DATA、CRC、EOF的數據段,生成符合FC幀格式的數據。在這之后,32:8復用模塊將32 bit并行輸入的數據復用成8 bit并行輸出的數據。隨后進入8 b/10 b編碼模塊,完成8 b/10 b的編碼工作并以10 bit位寬,106.25 MHz的速率送入VSC7145串并/并串芯片,最后以1.062 5 Gbs的速率輸出到SFP光收發模塊,由光收發模塊將電信號調制成光信號輸出。

在RX接收部分,由光收發模塊還原成的電信號通過VSC7145串并/并串芯片后以10 bit的并行數據形式輸入到FPGA中,由8 b/10 b解碼器解碼,輸出8 bit并行數據(在解碼過程中,解碼器可以通過判斷碼流的極性來判別是否在傳輸過程中出現誤碼)。8 b/10 b解碼輸出后的數據通過1個8:32解復用模塊解復用成32 bit的并行數據,并行支路速率為26.562 5 MHz,隨后32位并行數據通過FC幀檢測提取模塊,生成標識信號隨路輸出。在CRC校驗/判決模塊中,數據通過CRC位運算反映是否出現誤碼,并給出指示。在這之后,FC數據幀重組為IEEE1394數據幀,最后經由32:16復用模塊將32 bit并行IEEE1394幀數據重新復用成16 bit并行數據,與53.12 MHz的隨路信號一同送出FPGA芯片。

3 FPGA功能驗證

本設計已在Xilinx Spartan3系列的Xc3s200中實現,并在Xilinx ISE 7.1仿真環境下進行了功能和時序仿真驗證。采用偽隨機序列發生器生成的偽隨機代碼模擬IEEE1394數據源,設定每1 000 Byte為一個數據包包長。

3.1 功能仿真結果

1)在發送端,IEEE1394數據包被拆封,重組成FC數據幀,并由8 b/10 b編碼器編碼后輸出,如圖6中仿真波形tx_dtout,和TX_encode_ dtout所示。本文引用地址:http://www.104case.com/article/156204.htm

2)在接收端,FC幀結構被正確檢測并提取,在CRC校驗正確后重組成IEEE1394數據幀格式輸出,如圖7中仿真波形tx_dtout,crc32及rx_dtout所示。

經仿真測試,FPGA實現IEEE1394到FC數據幀格式的映射功能,各模塊均正常工作,數據通信良好,無丟包現象。

3.2 時序仿真結果

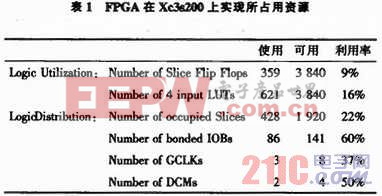

該設計在Xc3s200上實現后,FPGA所使用的資源如表1所示,整個系統資源占用率較低,最高運行速率能達到135.245 MHz,滿足106.25 MHz的片上最高運行速率要求,設計達到了預期結果。

4 結束語

光纖通道具有支持多種上層傳輸協議的優點,本文在已有工作的基礎上,利用FPAG,對所提出的IEEE1394到光纖通道的協議映射方案進行了硬件設計,通過FPGA功能仿真及時序仿真驗證了所提方案的可行性。利用此FPGA協議轉換模塊,本文還設計了基于FC的IEEE1394光信號傳輸系統,給出了具體的硬件設計方案。目前,此系統的主要調試工作已完成,后續的工作將通過系統傳輸實驗,對系統性能進行分析研究。

評論