基于光纖通道的IEEE1394光信號傳輸系統(tǒng)設(shè)計(jì)

對映射過程的說明:

1)目的節(jié)點(diǎn)和源節(jié)點(diǎn)地址由IEEE1394的16位擴(kuò)充到24位,使網(wǎng)絡(luò)規(guī)模變得比單一的IEEE1394網(wǎng)絡(luò)要大。

2)T-TYPE用來指明交換消息的傳輸特性,包括交換的傳輸方向和終端-終端(NT-NT)交換的性能定義。在NT-NT類型交換中,將為接收NT提供發(fā)送NT的地址,或者為發(fā)送NT提供接收NT的地址。

3)T—CTL用于實(shí)現(xiàn)FC網(wǎng)絡(luò)和IEEE1394網(wǎng)絡(luò)之間的消息傳輸,實(shí)現(xiàn)兩者之間的橋路連接,完成FC網(wǎng)絡(luò)終端或網(wǎng)絡(luò)控制器與IEEE1394節(jié)點(diǎn)之間的消息傳輸。

4)將IEEE1394中的幀頭CRC校驗(yàn)和數(shù)據(jù)CRC校驗(yàn)分開。在IEEE1394數(shù)據(jù)傳輸中,首先進(jìn)行的是幀頭CRC校驗(yàn),如果發(fā)現(xiàn)錯(cuò)誤,則立即拋棄該幀。所以這里設(shè)想將IEEE1394數(shù)據(jù)CRC放在光纖通道數(shù)據(jù)幀的可選幀頭,將幀頭CRC放在光纖通道數(shù)據(jù)幀CRC校驗(yàn)中,這樣可以先檢測幀頭CRC,節(jié)省系統(tǒng)開銷。

2 IEEE1394光信號傳輸系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

2.1 系統(tǒng)的構(gòu)架

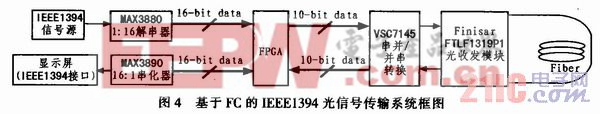

為在光纖通道傳輸IEEE1394信號,構(gòu)建兩種總線互連的硬件平臺,所設(shè)計(jì)的傳輸系統(tǒng)不僅要實(shí)現(xiàn)兩種數(shù)據(jù)幀格式的轉(zhuǎn)換,還要實(shí)現(xiàn)FC-0、FC-1、FC-2協(xié)議層中的部分功能。本文所設(shè)計(jì)的基于FC的IEEE1394光信號傳輸系統(tǒng)結(jié)構(gòu)如圖4所示,包括IEEE1394信號源,基于FPGA的1394-FC協(xié)議轉(zhuǎn)換器,必要的外圍接口器件以及光纖收發(fā)模塊,系統(tǒng)傳輸速率1.062 5 Gb/s。其中,光纖通道FC-0層的功能由光電轉(zhuǎn)換模塊和串并與并串轉(zhuǎn)換芯片實(shí)現(xiàn),而IEEE1394到FC數(shù)據(jù)幀映射及FC-1、FC-2層功能主要基于FPGA進(jìn)行硬件編程來實(shí)現(xiàn)。本文引用地址:http://www.104case.com/article/156204.htm

2.2 基于FPGA的功能模塊設(shè)計(jì)與實(shí)現(xiàn)

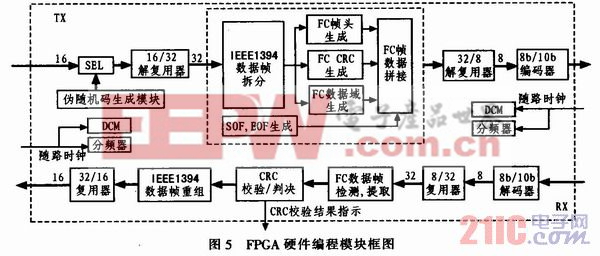

在所設(shè)計(jì)的系統(tǒng)中,F(xiàn)PGA主要實(shí)現(xiàn)IEEE1394到FC的數(shù)據(jù)幀映射以及FC-1、FC-2層功能。基于FPGA的功能模塊結(jié)構(gòu)如圖5所示。

1)FC-1層功能單元包括8 b/10 b編碼/解碼模塊和D/K類型指示模塊。

2)FC-2層功能單元包括數(shù)據(jù)接收模塊,發(fā)送模塊及系統(tǒng)配置模塊。

3)IEEE1394到FC的數(shù)據(jù)幀映射模塊(協(xié)議轉(zhuǎn)換)是FPGA設(shè)計(jì)的核心部分。該部分能夠完成對信號源發(fā)出的IEEE1394數(shù)據(jù)幀到FC協(xié)議的數(shù)據(jù)幀的映射工作,即將IEEE1394數(shù)據(jù)幀轉(zhuǎn)換為FC幀格式。同時(shí)能從接收到的FC數(shù)據(jù)幀還原出IEEE1394數(shù)據(jù)幀。

4)FPGA片內(nèi)的發(fā)送(TX)部分和接收(RX)部分均加入了數(shù)字時(shí)鐘管理(DCM)和分頻器模塊,DCM可以使時(shí)鐘信號通過時(shí)鐘樹達(dá)到各個(gè)片內(nèi)寄存器,以減小片內(nèi)時(shí)鐘信號的抖動(dòng)和延時(shí),提高系統(tǒng)運(yùn)行速率。

此外,為了方便在沒有外接IEEE1394信號源的情況下對FPGA內(nèi)部的功能模塊進(jìn)行調(diào)試,在FPGA的TX前通過采用線性反饋移位寄存器IP核構(gòu)建了一個(gè)偽隨機(jī)序列發(fā)生器,可以用來模擬IEEE1394數(shù)據(jù)源,并通過1個(gè)二選一選擇器實(shí)現(xiàn)外部輸入信號與內(nèi)部偽隨機(jī)序列的選擇功能。

評論