基于IEEE802.1 6e標準的LDPC編碼器設計與實現

3 LDPC編碼算法的實現

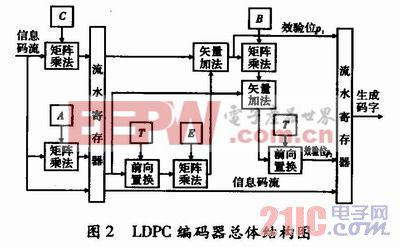

根據上述編碼算法,FPGA程序實現了0.5碼率,碼長為2 304 bit,信息位為1 152 bit數據流的編碼。每幀送入1 152 bit原始數據流,經過編碼后產生1 152 bit效驗位,因為是系統碼,所以將原始信息位后緊跟效驗位就可以合并成所要發送的編碼碼流。編碼器的硬件總體結構如圖2所示。本文引用地址:http://www.104case.com/article/156074.htm

從圖2可以看出,LDPC編碼器中主要包含矩陣乘法模塊,前項置換模塊,矢量加法模塊,以及生成碼字模塊。現對矩陣乘法模塊,前項置換模塊和碼字生成模塊進行介紹。

(1)矩陣乘法器模塊:主要由循環移位器和模二加法器組成。由于FPGA運算的并行特點,編碼器在計算矩陣乘法時可按行并行操作。輸入的原始信息比特流與效驗矩陣Hb的每一行進行相乘運算時,首先按照RAM中存儲的非零列號找到相對應的信息位中的矢量,并對該矢量進行循環右移,循環右移的次數依照IEEE802.11e標準的規定進行控制,然后把這一行中的所有非零元素和信息位相乘所得結果做一次異或操作,這就是矩陣的一行與信息位相乘的結果。該過程可以并行執行,同時完成矩陣中每一行與信息位的相乘運算。

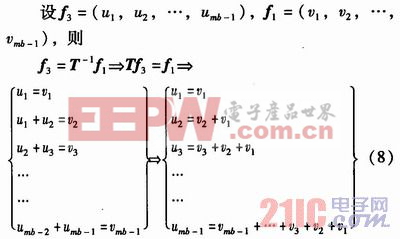

(2)前項置換器模塊:IEEE802.16e標準中規定,LDPC碼的效驗矩陣r是雙對角矩陣,所以對于乘矩陣T的逆的操作采用前項置換方法,其原理如下:

所以在FPGA中進行乘矩陣r的逆的計算,不必進行求逆和相乘運算,僅用異或運算就能完成。

(3)生成碼字模塊:主要作用是將原始信息位與效驗位p1和p2合成。在IEEE802.16e標準中規定LDPC碼為系統碼,所以將原始信息位與效驗位p1和p2按順序依次拼接起來,就是實際編碼后數據。

4 FPGA仿真結果分析

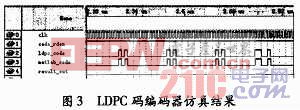

在QuartusⅡ軟件下進行編譯和綜合,器件選擇為Altera公司STRATIXII系列的EP2S90F1020C3,整個LDPC編碼器最高工作時鐘214 MHz,邏輯資源占用3 027 LE。LDPC碼編碼仿真結果如圖3所示。

code_rden:編碼器使能標志,高電平說明LDPC編碼器正在工作。

matlab_code:LDPC編碼的Matlab仿真結果輸出。

ldpc_code:LDPC編碼的FPGA仿真結果輸出。

result_out:比對Matlab與FPGA仿真結果,輸出碼流進行相減一直為零,說明仿真結果正確。

5 結束語

文中分析了基于IEEE802.16e標準的LDPC碼的校驗矩陣H,然后在QuartusⅡ平臺下根據分塊矩陣的快速編碼算法設計了一種編碼器,滿足IEEE802.16e標準的碼長為2 304,碼率為1/2的LDPC碼的編碼要求,并仿真驗證了LDPC編碼器的性能。仿真結果證明通過合理的構造LDPC碼的校驗矩陣以及選擇合適的編碼算法,可以有效降低編碼復雜度,并實現了線性編碼。

評論