基于Virtex-5的串行傳輸系統的實現

引言

本文引用地址:http://www.104case.com/article/155829.htm 隨著USB 3.0、SATA 3.0、PCI-E 2.0等新串行規范的發布以及更高速的串并/并串轉換單元(SERDES)芯片的推出引起了業界對高速差分串行數據傳輸的無限憧憬。為了解決下一代無線通信基站中多天線(MIMO)信號處理所帶來的巨大數據吞吐量要求,本文基于Virtex-5 FPGA的GTP單元給出了一種在高級電信計算架構(ATCA)機箱內實現單對差分線進行3.125Gbps串行傳輸的設計方案。

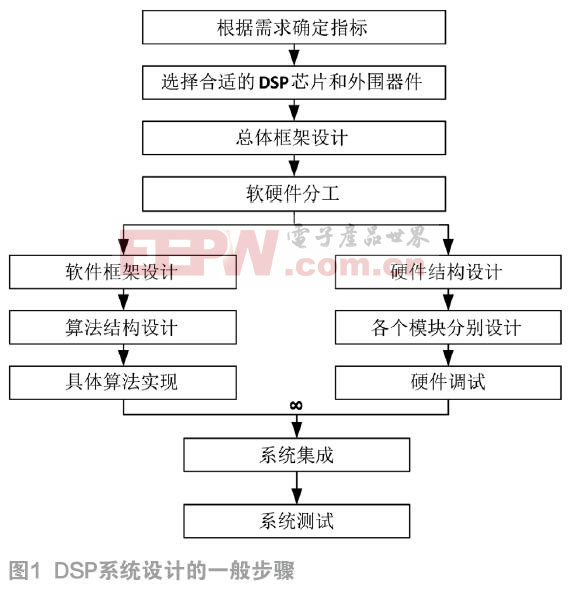

傳輸系統設計

傳輸系統的組成結構如圖1所示,主要由兩塊ATCA板和一塊ATCA機箱背板組成。兩塊ATCA板上各放置一片FPGA作為串行鏈路的兩個端點,兩片FPGA之間用兩對差分線進行連接,形成雙向各3.125Gbps的串行通信鏈路。為了驗證該系統的遠距離傳輸能力,將兩塊板放置在14槽ATCA機箱的物理槽位1和物理槽位14,此時總的傳輸距離大約為40英寸。

圖1 高速串行傳輸系統的總體結構

由于已有ATCA機箱的背板性能不可更改,本文主要的設計集中在ATCA單板的設計上,主要是單板的疊層設計、作為傳輸端點的FPGA的供電設計、串行傳輸的參考時鐘設計以及FPGA內部GTP收發器單元的參數調節。

疊層設計

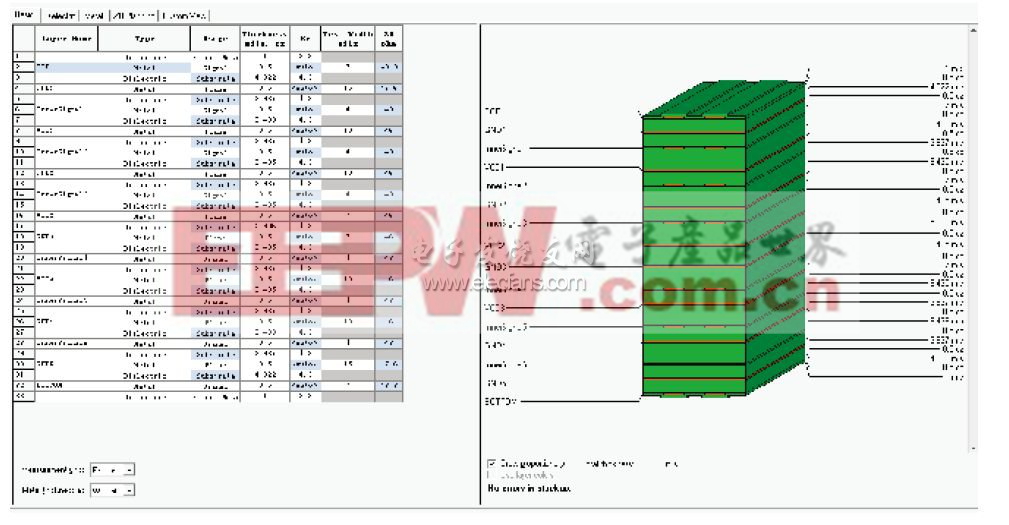

疊層設計是其他設計的基礎,本系統在設計疊層結構的時候主要考慮了兩個方面:一是讓所有的GTP收發差分線布于帶狀線信號層而不是單邊耦合的微帶線信號層。雖然帶狀線比微帶線損耗大一些,但是帶狀線的阻抗更可控一些,而且與交流地平面的耦合更好,有利于高速信號的回流;二是為了減少GTP單元的供電噪聲,采用三個電源平面分別給串行收發器的三種模擬電源AVTT(端接電源)、AVCC(內部電路電源)、AVPLL(PLL電源)進行供電。具體的疊層結構如圖2所示。

圖2 疊層結構的設計

電源設計

GTP模擬供電電源的噪聲情況是影響GTP性能的重要因素之一。除了在設計疊層的時候讓GTP的三個模擬電源分別分配到一個單獨的平面上并配上地平面進行耦合外,還在外部為每個電源管腳都串聯一個磁珠,再并聯一個0.22μf的電容形成一個LC低通濾波器對電源進行濾波。GTP的模擬電源都采用低噪聲的LDO電源芯片TPS74401進行供給,輸出電壓的紋波小于50mV。

時鐘設計

高速串行收發器的參考時鐘是另一個影響信號傳輸質量的重要因素。本系統使用具有強大clock clean功能的時鐘合成芯片LMK03001C來產生串行收發器的參考時鐘。其輸出時鐘的最大均方根抖動(RMS jitter)小于550fs,占空比為50%,輸出時鐘電平標準具有LVDS和LVPECL兩種。其輸出時鐘的頻率可以靈活編程設置,從而可以滿足不同傳輸速率的要求,使本系統可以適應多種串行傳輸協議的實現。

低通濾波器相關文章:低通濾波器原理

評論