基于DDS跳頻信號(hào)源的設(shè)計(jì)與實(shí)現(xiàn)

3.2 基于FPGA跳頻信號(hào)仿真結(jié)果

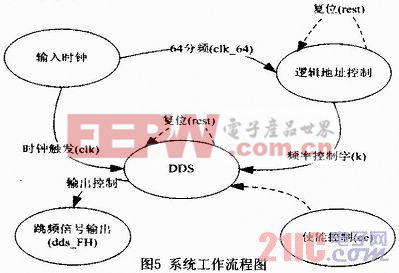

圖2中給出了基于本設(shè)計(jì)DDS跳頻信號(hào)生成的總體設(shè)計(jì)圖。共由四部分組成:系統(tǒng)時(shí)鐘、分頻器、邏輯地址控制單元及DDS單元。跳頻信號(hào)的產(chǎn)生是通過(guò)隨機(jī)地改變頻率控制字來(lái)達(dá)到改變信號(hào)的輸出頻率,圖5給出了系統(tǒng)工作流程圖。本文引用地址:http://www.104case.com/article/155539.htm

如圖5所示,系統(tǒng)時(shí)鐘clk經(jīng)過(guò)64分頻得到clk_64。邏輯控制單元由6級(jí)移位寄存器構(gòu)成。在每個(gè)clk_64上升沿到來(lái)時(shí),邏輯控制單元將產(chǎn)生一個(gè)6位的頻率控制字(k)。當(dāng)DDS使能信號(hào)ce為高電平時(shí),DDS將停止工作。當(dāng)ce為低電平時(shí),在clk上升沿時(shí)DDS被觸發(fā),在當(dāng)前狀態(tài)下k的控制下,得到相應(yīng)地址所對(duì)應(yīng)的信號(hào)幅值。當(dāng)k沒(méi)有變化時(shí),DDS輸出正弦信號(hào)的頻率沒(méi)有任何變化,在一個(gè)clk_64上升沿到來(lái)時(shí),k發(fā)生變化,從而使得DDS輸出的正弦信號(hào)的頻率發(fā)生變化。當(dāng)復(fù)位信號(hào)reset為高電平時(shí),邏輯地址控制單元和DDS單元同時(shí)回到初始狀態(tài),并保持不變,輸出端dds_FH輸出一直為零。當(dāng)reset變?yōu)榈碗娖綍r(shí),在一個(gè)clk上升沿時(shí)系統(tǒng)開(kāi)始工作。

為方便觀察仿真結(jié)果,本設(shè)計(jì)采用ModelSim SE 6.1d作為仿真波形測(cè)試軟件。通過(guò)3.1節(jié)分析,由于本設(shè)計(jì)的DDS所產(chǎn)生的頻率性能穩(wěn)定,且跳頻信號(hào)的誤差并不累加。因此本節(jié)只給出仿真結(jié)果,不做其性能分析。圖6為基于DDS的跳頻信號(hào),圖6給出圖5中各個(gè)控制信號(hào)的仿真結(jié)果。表2中給出圖6中不同頻率控制字所對(duì)應(yīng)的正弦信號(hào)的頻率與理論值的對(duì)比,可以看出本設(shè)計(jì)的DDS與理論值的誤差較小。由于ROM中存儲(chǔ)的點(diǎn)數(shù)較少,更加節(jié)省資源。

4 結(jié)束語(yǔ)

在FPGA硬件平臺(tái)下設(shè)計(jì)基于DDS的跳頻信號(hào)產(chǎn)生系統(tǒng),不僅實(shí)現(xiàn)了大量數(shù)據(jù)快速運(yùn)算,提高了仿真的速度,而且可以靈活、重復(fù)地對(duì)系統(tǒng)的參數(shù)進(jìn)行優(yōu)化配置,便于提高跳頻系統(tǒng)的性能。本文所設(shè)計(jì)的DDS,結(jié)構(gòu)簡(jiǎn)單、硬件資源占用率少,且產(chǎn)生頻率相對(duì)準(zhǔn)確。根據(jù)對(duì)所需跳頻信號(hào)精確度要求的不同,合理配置參數(shù),協(xié)調(diào)硬件資源與頻率準(zhǔn)確之間的矛盾關(guān)系,最終實(shí)現(xiàn)跳頻系統(tǒng)的最優(yōu)配置。

評(píng)論