利用S參數對RF開關模型進行高頻驗證

傳輸線路設計

傳輸線路的阻抗由線路上的電感和電容的比值設置。圖3所示為一個簡單的傳輸線路模型。

圖3. 傳輸線路的集總元件模型

利用計算目標頻率時的復阻抗的公式,確定獲得特定阻抗所需的L和C的值。調整L和C的方式取決于傳輸線路模型的類型,最常用的模型是“微帶線”和“共平面波導”模型。利用物理參數,例如從走線到地層的距離、走線寬度和PCB基板介電常數等,可以平衡電感和電容,從而提供所需的阻抗。設計傳輸線路阻抗的最簡單方法是使用阻抗設計程序,此類程序有很多。

測量阻抗

設計并生產出傳輸線路后,必須測量其阻抗,以驗證設計和實施無誤。一種測量阻抗的方法是使用時域反射(TDR)。TDR測量可以反映PCB走線的信號完整度。TDR沿著信號線發送一個快速脈沖,并記錄反射情況,然后利用反射信息計算距離信號源特定長度處的路徑阻抗。利用阻抗信息可以找到信號路徑中的開路或短路,或者分析特定點的傳輸線路阻抗。

TDR的工作原理是:對于一個不匹配的系統,在信號路徑上的不同點,反射會與信號源相加或相減(相長和相消干涉)。如果系統(本例中為傳輸線路)匹配50 ,則信號路徑上不會發生發射,信號保持不變。然而,如果信號遇到開路,反射將與信號相加,使之加倍;如果信號遇到短路,反射將通過相減與之抵消。

如果信號遇到一個端接電阻,其值稍高于正確的匹配阻抗,則在TDR響應中會看到一個凸起;若端接電阻值稍低于匹配阻抗,則在TDR響應中會出現一個凹陷。對于容性或感性端接,將看到相似的響應,因為電容在高頻時短路,電感在高頻時開路。

在所有影響TDR響應精度的因素中,最重要的一個是沿信號路徑發送的TDR脈沖的上升時間。脈沖的上升時間越快,則TDR可以分辨的特征越小。

根據TDR設備設定的上升時間,系統可以檢測的兩個不連續點之間的最短空間距離為: (9)

(9)

其中:

lmin = 從信號源到不連續點的最短空間距離

c0 = 光在真空中的傳播速度

trise = 系統的上升時間

εeff = 波在其中行進的介質的有效介電常數

若是檢測相對較長的傳輸線路,20 ps到30 ps的上升時間即足夠;但若要檢測集成電路器件的阻抗,則需要比這快得多的上升時間。

記錄TDR阻抗測量結果有助于解決傳輸線路設計的各種問題,如錯誤的阻抗、連接器結點引起的不連續以及焊接相關問題等。

精確記錄S參數

一旦完成PCB和系統的設計與制造,就必須在設定的功率和一系列頻率下利用VNA記錄下S參數;VNA應經過校準,確保記錄的精確性。校準技術的選擇取決于多種因素,如目標頻率范圍和待測器件(DUT)所需的參考平面等。

校準技術

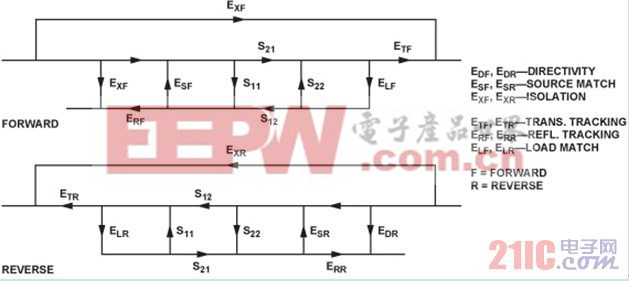

圖4顯示了雙端口系統的完整12項誤差模型及其系統性影響和誤差源。測量頻率范圍會影響校準選擇:頻率越高,則校準誤差越大。隨著更多誤差項變得顯著,必須更換校準技術以適應高頻影響。

圖4. 完整的雙端口12項誤差模型

評論