USB 2.0主控器軟硬件協同仿真系統設計

3 基于本驗證系統的USB主控器驗證過程

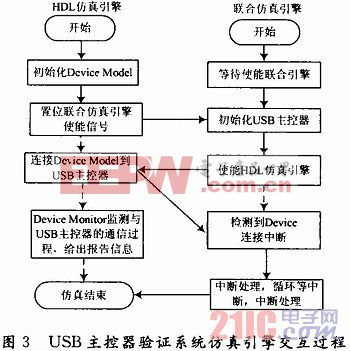

由于使用了聯合仿真引擎,測試激勵既可以使用Verilog HDL編寫也可以使用C語言編寫。運行C語言編寫的測試激勵時,需要在測試平臺中預先置位使能信號打開聯合仿真引擎,觸發仿真工具(如NCVerilog)調用C測試激勵程序的主函數。在C測試激勵順序執行時,整個RTL的仿真時間會停在當前時刻。只有當C測試激勵調用了基本的讀/寫函數、中斷響應之類的底層函數,硬件仿真時間才會向前推進,RTL仿真器繼續往前運行。直到RTL反饋后,C測試激勵程序才會繼續往下一行執行。USB主控器驗證系統仿真引擎交互過程如圖3所示。本文引用地址:http://www.104case.com/article/155203.htm

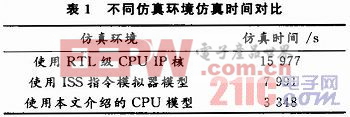

具體過程包括:HDL仿真工具執行Verilog HDL描述的USB的外設模型初始化過程;HDL仿真工具使能聯合仿真引擎,測試用例進入聯合仿真引擎繼續執行;聯合仿真引擎初始化待驗證USB主控器;聯合仿真引擎執行特定API函數.測試用例進入HDL仿真過程;通過調用外設的atta tch命令,使外設模型連接到待驗證的USB主控器;聯合仿真引擎等待外設模型連接中斷,停止在當前時刻,直到中斷有效;聯合仿真引擎執行外設模型連接中斷處理;測試用例繼續執行HDL仿真過程。主控器與外設模型按照配置速度,傳輸類型,傳輸方向,傳送的數據包的工作速度;C驅動循環等待中斷信號有效,進行中斷處理。AHB監控器、AXI監控器和USB監控器監測主控器AHB端和USB端的工作,進行協議檢查,給出報告信息,仿真過程可以通過日志文件方便監測。基于上述思路編寫的驗證USB主控器各個不同功能的測試用例,在不需要使用任何PLI(編程語言接口)函數的情況下,能夠快速、方便地實現USB 2.0主控器各個不同層級的Driver的功能,從而保證能夠全面的驗證此主控器的特性。表1是在不同的仿真環境下,測試USB主控器與外設進行進行高速傳輸2 Mb數據所需要的時間。從表中可以看出,系統中使用RTL級CPU IP核的系統,仿真速度最慢;基于ISS指令集模擬器的仿真系統,速度次之;本環境的仿真速度最快。

4 結語

本文設計的用于USB主控器IP驗證的軟硬件協同仿真系統具有仿真速度快、仿真系統資源占用小、減少軟硬件集成驗證測試的時間的特點,經實踐證明,效果良好。通過使用本系統,軟件人員能在硬件設計驗證的早期就能進入IP的軟件硬件聯調,縮短了研發時間。同時,本系統具有良好的可重用性,對其他IP的驗證同樣有效,可為其他IP的驗證提供參考。

評論