USB 2.0主控器軟硬件協(xié)同仿真系統(tǒng)設(shè)計(jì)

2.2 本文設(shè)計(jì)的軟硬協(xié)同仿真系統(tǒng)介紹

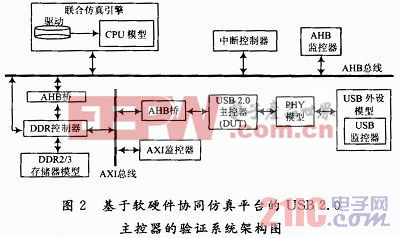

相對(duì)使用傳統(tǒng)驗(yàn)證方法,本文設(shè)計(jì)的軟硬件協(xié)同仿真系統(tǒng)使用抽象度較高的C語言編寫測(cè)試激勵(lì),通過調(diào)用系統(tǒng)中CPU模型對(duì)外提供的API完成激勵(lì)生成與響應(yīng)檢查。基于本引擎編寫的測(cè)試激勵(lì)可以方便的移植,所以在硬件仿真階段就能調(diào)試SoC系統(tǒng)軟件,不必等到FPGA平臺(tái)設(shè)計(jì)完成或芯片設(shè)計(jì)完成后,從而大大節(jié)省了項(xiàng)目開發(fā)時(shí)間。圖2是本文驗(yàn)證USB主控器功能的軟硬件協(xié)同仿真的系統(tǒng)架構(gòu)圖。本驗(yàn)證環(huán)境由3大部分組成:聯(lián)合仿真引擎,即CPU模型;總線架構(gòu)及系統(tǒng)內(nèi)存模塊,包括一個(gè)DDR模型和DDR控制器;USB協(xié)議實(shí)現(xiàn)、檢查模塊,包括待驗(yàn)證的USB主控器、支持UTMI+接口的PHY、外設(shè)模型。在該平臺(tái)下,聯(lián)合仿真引擎(CPU模型)替換掉SoC中原有的CPU,是整個(gè)驗(yàn)證系統(tǒng)的核心也是整個(gè)系統(tǒng)設(shè)計(jì)的核心。通過使能信號(hào)觸發(fā)聯(lián)合仿真引擎工作來執(zhí)行C程序,將軟件對(duì)USB主控器的控制轉(zhuǎn)化成總線時(shí)序,將軟件和硬件交互的行為模擬到RTL側(cè)。下文將對(duì)仿真平臺(tái)中各個(gè)模塊,重點(diǎn)對(duì)聯(lián)合仿真引擎進(jìn)行詳細(xì)介紹。本文引用地址:http://www.104case.com/article/155203.htm

2.2.1 基于TLM建模的聯(lián)合仿真引擎及設(shè)計(jì)

使用軟硬件協(xié)同仿真的方法驗(yàn)證USB主控器,只需要用C語言編寫USB主控器驅(qū)動(dòng)并將其集到成系統(tǒng)中進(jìn)行仿真測(cè)試,因此要求CPU模型能夠簡(jiǎn)單、高效地執(zhí)行驅(qū)動(dòng)程序,CPU在SoC中都是直接通過AHBMaster接口連接到總線(BUS)上,對(duì)SoC中要驗(yàn)證的IP來講,CPU就是一個(gè)總線Mas ter,IP并不關(guān)心CPU是什么指令集,采用何種方式實(shí)現(xiàn)。基于此,本聯(lián)合仿真引擎設(shè)計(jì)的CPU模型并沒有采用基于特定指令集設(shè)計(jì)的復(fù)雜方法,而是采用基于SystemC事物級(jí)建模(TLM)技術(shù)構(gòu)造了一個(gè)基于AHB協(xié)議的總線功能模型(BFM),實(shí)現(xiàn)了對(duì)CPU對(duì)SoC中其他模塊所呈現(xiàn)的AHB Master接口的時(shí)序封裝。這個(gè)BFM能和要驗(yàn)證的RTL模塊進(jìn)行連接和通信,它能夠編譯并解釋基于C語言編寫的驅(qū)動(dòng)程序,并把這個(gè)驅(qū)動(dòng)程序要執(zhí)行的操作翻譯成對(duì)應(yīng)的AHB總線信號(hào)。通過層次化的封裝,本聯(lián)合仿真引擎把基于時(shí)鐘時(shí)序精度的RTL的抽象層提升到?jīng)]有任何時(shí)鐘和時(shí)間概念的軟件抽象層。同時(shí),本引擎能取代任何CPU。不管SoC中真正使用的CPU是MIPS指令集、ARM指令集還是其他CPU,都能被本聯(lián)合仿真引擎替代。

本引擎的CPU模型使用系統(tǒng)仿真用的工作站或者服務(wù)器的宿主CPU來運(yùn)行驗(yàn)證工程師編寫的基于C語言的測(cè)試激勵(lì)程序,將需要的具體硬件行為通過Channel向下傳送到RTL端。相對(duì)于直接使用SoC中CPU IP核的RTL的仿真,該引擎省去了CPU IP核取指令和運(yùn)行指令的復(fù)雜的仿真、運(yùn)算過程,大大節(jié)省了仿真運(yùn)行的時(shí)間。本聯(lián)合仿真引擎為軟件人員和硬件驗(yàn)證人員分別提供了一些總線訪問和中斷處理的API,為了滿足硬件驗(yàn)證的需要,另外設(shè)計(jì)了一些API可以實(shí)現(xiàn)讓系統(tǒng)等待一定時(shí)鐘周期或者時(shí)間、停止或重新開始仿真、不通過總線而可以快速訪問系統(tǒng)存儲(chǔ)器等功能。在系統(tǒng)中CPU模型對(duì)USB主控器和DDR控制器的配置均通過這2個(gè)模塊對(duì)外提供的AHB Slave接口。

2.2.2 仿真系統(tǒng)的其他模塊介紹

DDR2/3為系統(tǒng)內(nèi)存,存儲(chǔ)USB主控器正常工作需要的描述符和收發(fā)的數(shù)據(jù)。由于本系統(tǒng)中DDR2/3控制器只提供AXI Slave的數(shù)據(jù)接口,系統(tǒng)中CPU和USB主控器需要通過AHB橋?qū)HB從機(jī)的接口時(shí)序轉(zhuǎn)換成AXI Master的接口時(shí)序,保證2個(gè)模塊之間正常的數(shù)據(jù)通信。系統(tǒng)工作過程中AxI,AHB總線監(jiān)控器監(jiān)控2個(gè)總線活動(dòng),打印出報(bào)告信息,方便仿真結(jié)果檢查。

USB主控器是待驗(yàn)證的主控器(DUT)。PHY模型提供UTMI+接口,有USB 2.0和USB 1.1兩種接口分別支持EHCI接口和OHCI接口實(shí)現(xiàn)。外設(shè)模型包括一個(gè)PHY驗(yàn)證IP(VIP)和一個(gè)USB外設(shè)驗(yàn)證IP,模擬USB外設(shè)的行為。USB外設(shè)VIP中包含一個(gè)USB監(jiān)控器模型,負(fù)責(zé)協(xié)議檢查,記錄事物傳輸進(jìn)程,監(jiān)控高速、全速和低速的USB傳輸,提供數(shù)據(jù)包級(jí)和事物級(jí)傳輸?shù)谋O(jiān)控,同時(shí)可以監(jiān)控掛起、恢復(fù)和復(fù)位信號(hào)。

評(píng)論