源同步信號跨時鐘域采集的兩種方法

異步FIFO采集法

再說異步FIFO采集法,其實這種方法沒什么新奇,只不過充分利用異步FIFO的同步特性來完成跨時鐘域的數據交互。但是其中還是有幾個非常關鍵的要點需要提醒設計者注意,無論如何FIFO的輸入端數據和時鐘信號(包括控制信號,如有效使能信號等)必須符合FIFO的數據鎖存有效建立和保持時間,這個最重要的條件除了需要靠數據源端來保證外,還需要靠數據鎖存端(FPGA內部)設計者做好時序上的約束和分析,否則到源端再nice的波形恐怕都無法保證能夠可靠的被FIFO鎖存。

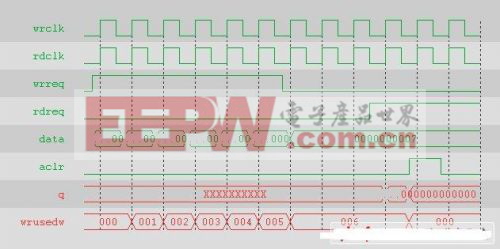

異步FIFO的基本通訊時序波形如圖5所示。我們關心的是FIFO的寫入。由圖中不難發現,寫入時鐘wrclk的每個上升沿會判斷寫入請求信號wrreq是否有效,若是有效則FIFO會相應的鎖存當前的寫入數據data。簡單來看,從基本時序上分析,wrclk的上升沿需要對準wrreq和data的中央,這是外部傳輸過來的源信號必須滿足的基本關系。無論如何,即便是絞盡腦汁,也要想辦法讓這個基本關系得到保證,否則,后面的rdclk、rdreq配合的再默契恐怕都不能得到穩定的q輸出。

圖5

原型開發的前期,設計者必須首先驗證寫入信號的關系,哪怕是不惜動用示波器(⊙n⊙b汗,連示波器都沒有不要混了),源端給到FPGA輸入端口的信號很多時候不是那么盡善盡美的,實踐出真知,測試結果說了算。當然了,實在沒有先進武器又想打勝仗的朋友恐怕只有不停的用代碼測試采集到最穩定的數據了,這有點碰運氣的成分在里面,不是非常推薦。

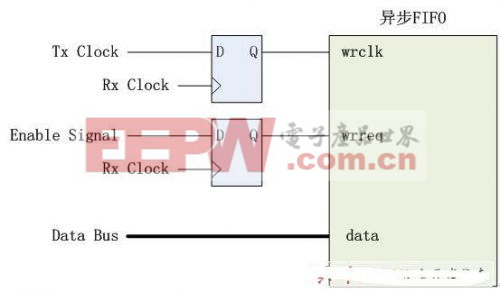

類似與開篇提到的應用,特權同學的實際信號采集如圖6所示,把寫入時鐘Tx Clock和寫入請求信號Enable Signal都先用同步時鐘Rx Clock打了一拍,然后再輸入FIFO中,而數據總線Data Bus則直接送往FIFO。這樣從最終檢測來看,能夠保證時鐘的上升沿對準數據和控制信號的中央,相對穩定和安全的把數據送往FIFO中。

圖6

工程實踐中往往不是一招一式的生搬硬套理論,一定要抓住最關鍵的設計要點,并采取各種有效的手段保證設計的實現。

脈沖點火器相關文章:脈沖點火器原理

評論