源同步信號跨時鐘域采集的兩種方法

對于數據采集接收的一方而言,所謂源同步信號,即傳輸待接收的數據和時鐘信號均由發送方產生。FPGA應用中,常常需要產生一些源同步接口信號傳輸給外設芯片,這對FPGA內部產生時鐘或數據的邏輯和時序都有較嚴格的要求。而對于一些FPGA采集信號的應用中,常常也有時鐘和數據均來自外設芯片的情況,此時對數據和時鐘的采集也同樣需要關注FPGA內部的邏輯和時序。當然,無論何種情況,目的只有一個,保證信號穩定可靠的被傳送或接收。

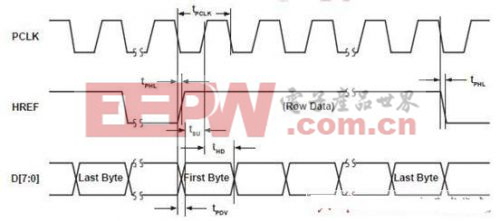

本文引用地址:http://www.104case.com/article/155011.htm對于一個如圖1所示的某視頻芯片產生的源同步信號,當FPGA對其進行采集同步到另一個時鐘域時,特權同學通常的做法有兩種,特權同學稱之為脈沖邊沿檢測采集法和異步FIFO采集法。下面簡單的對這兩種方法做一些討論和說明。

圖1

脈沖邊沿檢測采集法

脈沖邊沿檢測采集法,顧名思義,一定是應用了經典的脈沖邊沿檢測法來幫助或者直接采集信號。對于脈沖邊沿檢測法,大家可以參考特權同學的《深入淺出玩轉FPGA》或者用gooogle擺渡一下。而這里尤其需要提醒大家注意的是,著名的奈奎斯特采樣定理告訴我們:要從采樣信號中無失真的恢復原信號,采樣頻率應大于兩倍信號最高頻率。而特權同學通過實踐得出的結論與此相仿:若想穩定有效的采集到脈沖(數字信號)變化的邊沿,采樣頻率應大于被采樣脈沖最大頻率的3倍。注意是要大于3倍,甚至若是可能盡量采用4倍以上的采樣頻率才能夠達到穩定的狀態。至于為什么,我想深諳此道(脈沖邊沿檢測法)的聰明人看完結論就已經明白了,無需特權同學再廢話解釋一番。

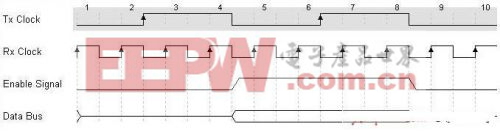

而具體的做法也很簡單,把圖1理想化就如圖2所示。其中,待采集信號時鐘Tx Clock,待采集數據使能信號Enable Signal,待采集數據總線Data Bus。FPGA內部信號采集時鐘為Rx Clock,該時鐘為待采集時鐘的4倍。

圖2

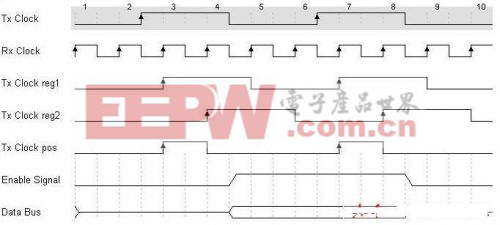

采用脈沖邊沿檢測法,使用Rx Clock去采集Tx Clock,Rx Clock reg1和Rx Clock reg2分別為第一級和第二級Tx Clock鎖存信號。Tx Clock上升沿對應的一個有效指示信號Tx Clock pos每個Tx Clock時鐘周期產生一個Rx Clock脈寬的有效高電平使能信號。從圖3中可以看到,此時若用Tx Clock pos作為FPGA內部采樣使能信號,雖然Tx Clock pos處于第7個Tx Clock,但是真正采集Data Bus其實已經是第8個Tx Clock上升沿了。很明顯,第8個Tx Clock上升沿對準的不是Data Bus的穩定信號中央,數據很可能采集到錯誤值。

圖3

因此,通過上面的分析,還是可以采取一些變通的方式來保證第8個Tx Clock上升沿采集到Data Bus的中央值。如圖4所示,采用同樣的方式對Data Bus做兩級信號鎖存,那么第8個Tx Clock上升沿就能夠在Data Bus reg2的中央采集數據了。這樣做只有一點小問題,相應的需要多付出2組寄存器來鎖存Data Bus。

圖4

脈沖點火器相關文章:脈沖點火器原理

評論