中頻信號處理板的設計與實現

1.1 DSP部分

本設計采用兩個DSP的方式,其中DSPTMS320C6713為浮點數字信號處理器,DSPTMS320C6415為定點數字信號處理器。TI的C67x和C64系列芯片都是非常成熟的DSP,其具有體積小、高速度、低功耗的特點,而且應用廣泛,開發難度較低。器件容易獲得。其中TMS320C6713是當前在軍工領域廣泛采用的浮點處理器,其最高支持300 MHz主頻,工業級器件支持200 MHz,其內核采用超長指令字(VLIW)體系結構,有8個功能單元、64個32 b通用寄存器。一個時鐘周期同時執行8條指令,運算能力最高可達到1600 MIPS/1200 FLOPS,支持雙精度的數據類型。TMS32 0C6415最高支持1 GHz,能穩定工作在480 MHz,內核采用超長指令字(VLIW)體系結構,有8個功能單元、64個32 b通用寄存器。一個時鐘周期同時執行8條指令,運算能力最高可達到4 800 MIPS。

在本設計中采用一顆TMS320C6713作為用戶系統處理核心。DSP的外部存儲器接口EMIF都需要掛接片外存儲器。TMS320C6713有一組EMIF總線,位寬分別為32 b。TMS320C6415作為信號處理和控制處理核心。一顆TM$320C6415有兩組EMIF總線,位寬分別為32 b。根據需要兩個DSP掛接有如下片外存儲器:

TMS320C6713需要掛接有如下片外存儲器:

SDRAM:128 Mb/片,采用MT48LC4M32,EMIFA接口,32位同步存儲器模式,100 MHz時鐘速度。

TMS320C6415需要掛接有如下片外存儲器:

FLASH:16 Mb/片,采用Am29DL160D,EMIF-B接口,8位異步存儲器模式,90 ns操作速度。

SDRAM:256 Mb/片,采用EMIF-A接口,32位同步存儲器模式,100 MHz時鐘速度。

2顆DSP的EMIF總線除了和外部存儲器連接外,還和FPGA的I/O相連,利用FPGA內部構建的雙口RAM或者FIFO進行數據的傳輸。傳輸支持EDMA方式。為獲得更好的數據吞吐速度,將外部存儲器和FPGA構建存儲器映射到不同的CE片選空間。

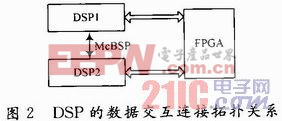

2顆DSP之間的數據通過FPGA進行交換,也可通過兩個DSP之間的McBSP實現兩顆DSP直接的數據交互,如圖2所示。本文引用地址:http://www.104case.com/article/154750.htm

在工程實現上,利用DSP內部的McBSP中斷,可以讓數據的交互在中斷服務程序里面完成,使DSP的響應更為快捷。

1.2 FPGA部分

本設計中采用Altera公司的EP3S110作為實時信號處理核心。EP3S110是Altera公司具有全新架構的高密度產品。它采用65 nm工藝,與前期產品相比,器件的邏輯密度是前者的2倍,功耗降低了50%,性能提高了25%。本設計中采用的芯片,片上LVDS總線最高速率可以達到1.25 Gb/s,該芯片集成了106 500LE,896個18×18乘法器,16個全局時鐘網絡,88個等效LVDS通道,片上RAM為9 Mb的容量。該芯片在設計中主要完成的功能有中頻信號的調制解調、編解碼、頻率點的置入、LVDS通路的建立、內部雙口的構建等功能。

1.3 A/D,D/A部分

本設計中采用4通道高速A/D和1通道D/A,A/D采用14 b 105 MSPS的高動態、高精度、快速轉換芯片,接收時4路A/D同時采集,滿足對中頻信號的采集要求,保證A/D的SNR在65 dB以上,D/A采用16 b 160 MSPS的高速數/模轉換器,1路模擬輸出,保證輸出的雜散較低,頻譜較純。

采用的芯片為ADS6445和AD9957。ADS6445的主要特點為:

(1)高采樣速率,采樣速率高達125 MSPS。

(2)高分辨率(14位)。

(3)時鐘輸入可以使用LVCMOS,LVPECL,LVDS方式。

(4)ADS6445既有粗略增益調整也有精細增益調整。

AD9957的主要特點為:

(1)32位相位累加器。

(2)波特率高達25 Mb/s的SPI接口。

(3)內置1 024×32的RAM,可實現內部調制功能。

(4)內部采用1.8 V供電,超低功耗。

(5)內置的低噪聲參考時鐘倍頻器允許使用低成本,低頻率外部時鐘作為系統時鐘,同時可提供優良的動態性能。

(6)支持測試向量和幅度斜坡式控制功能。

1.4 CPLD和時鐘部分

CPLD采用Altera公司的EPM2210F324來實現設計中的時鐘綜合器的配置和FPGA與DSP程序的加載等功能。整板正常上電后通過SPI配置時鐘綜合器,產生整板所需的時鐘,配置完成后,CPLD控制FPGA采用FPP方式從FLASH中加載程序,當FPGA加載成功后,根據FPGA的配置引腳CONFI GDONE狀態,將FLASH控制權交給DSP(6713),控制完成DSP(6713)的程序加載,然后控制DSP(6415)的程序加載。

時鐘電路采用內部10 MHz恒溫晶振和外部10 MHz原子鐘的雙時鐘設計,兩種時鐘通過時鐘綜合器AD9522完成切換。雙時鐘的設計保證了整板的穩定性,正常工作時使用外時鐘。當兩個時鐘有任一出現問題時,能快速切換到另一時鐘繼續穩定地工作。

評論