L波段直接數字式快跳頻率合成器設計

3 L波段快跳頻率合成器的實現方法

L波段快跳頻率合成器的原理方框如圖5所示。主要由晶體振蕩器、控制電路、DDS芯片、倍頻器,帶通濾波器、功率放大器等電路組成。本文引用地址:http://www.104case.com/article/154532.htm

高穩定度晶體振蕩器確保了頻率合成頻譜的高分辨率以及所需要的跳頻速度。設計中我們選用了溫度補償晶體振蕩器作為DDS的參考頻率源,它具有體積小、功耗低、高頻率穩定度和高頻譜純度等特性。

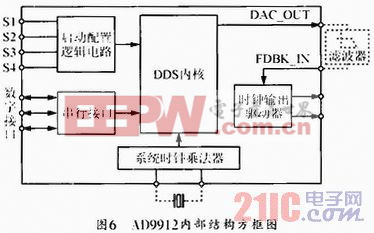

DDS芯片是產生跳頻的關鍵器件,選用了AD公司的AD9912。該器件以其集成度高,功能齊全,性能桌越,設計方便等優點而倍受人們的青睞AD9912內部結構方框圖如圖6所示。

AD9912電路具有如下特點:

(1)可提供最大1GSPS內部時鐘速率;

(2)14位內部集成D/A轉換器;

(3)48位頻率調節字;

(4)靈活的系統時鐘輸入,可接受晶振時鐘或外部參考時鐘。

由于AD9912器件輸出功率較低,在送入下級倍頻之前須經過放大濾波,得到所需的功率電平和頻譜純度的頻率。

倍頻部分選用Mini公司的四倍頻器,它可將DDS輸出的頻率倍至我們所需要的L波段,由于它的差損為24~30dB,我們還要使用一級放大濾波,最終得到我們所需的功率電平和頻譜純度的頻率放大和濾波電路采用現成集成電路,這樣可以減少的調試難度,方便大規模生產,中間加入π型衰減器,用以調整輸入輸出信號,使它們工作在正常范圍。

在完成功能的情況下,電路設計中盡量減少不必要的雜散干擾信號,我們還需要考慮以下幾方面問題:

(1)數字電路的抗干擾

數字電路具有系統時鐘、高速總線等大功率數字信號,所以它是一個較大的干擾源。對本身雜散就較大的DDS系統來說,解決數字電路部分的干擾是非常重要的。相關的元件盡量放得靠近些使各部件間的引線盡量短。在布局上根據模擬信號部分,數字電路部分,噪聲源要分開布局的原則,合理分區布置模擬信號通路,并口輸出控制信號以及噪聲源器件,減小相互之間的信號耦合。

對于頻率源電路,首先元件的性能要穩定,量值要準確,采用優質元件。布線時,電路盡量靠近地,連線要短而粗。如果可能,可以用地線包圍振蕩電路,晶振電路遠離DDS的輸出端,兩者垂直布線,避免靠近大電流信號線,并且遠離發熱元件。對于總線的布線,數據線、地址線、控制線盡量縮短,以減小對地分布電容;而且其長短和走線方式盡量一致,以免造成各線阻抗差異過大。如果是雙面走線,一定要使兩面的線盡量垂直,以防總線間的電磁串擾。同時,對于控制線需要在其上添加對地濾波電容,以及防止線上信號毛刺造成誤判。

(2)接地

在高頻電路的設計中,應該采用多點接地的方法。電子設備中接地點都直接接到距它最近的接地面上,以使接地的引線最短。這樣使得接地線上可能出現的高頻駐波現象顯著減少。各器件就近接地,就避免了在地線上形成干擾。在整塊板上采用多點,大面積就近接地,以縮短電流回路,同時走線中盡量加粗了接地線,以防止接地電位隨電流的變化而變化,致使電平不穩,抗噪

聲性能下降。

在數模混合的電路中,由于數字部分干擾很多,所以模擬部分易受影響,數字地和模擬地分割開,才能實現數字地和模擬地之間的隔離。

在敏感模擬信號線兩邊加上保護地,隔離噪聲和干擾。

減少輸入輸出間的串擾、如在DDS、濾波器等器件的輸入輸出信號間采用了輸入輸出垂直走線,用地線隔離屏蔽等措施。

評論