音頻信號數字化光纖傳輸實驗儀信道的設計與實現

3 軟件設計及仿真介紹

系統采用VerilogHDL語言進行程序編寫,在QuartusⅡ環境下編輯仿真。FPGA內部時鐘由18.432 MHz的有源晶振提供。FPGA的工作是:

1)提供D/A轉換芯片CS4334,A/D轉換芯片CS5342,并串轉換芯片LV1023的工作時鐘和串并轉換芯片LV1224的參考時鐘,其值均為18.432 MHz。

2)發送端對數據進行8B10B編碼,并將轉換后的數據傳送給串化器;接收端獲取串并轉換后的十位數據,進行解碼,還原為編碼前的八位數據,并將解碼后的數據傳送給數模轉換芯片。

3.1 8B10B編解碼

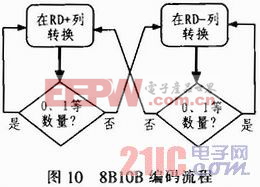

8B10B編碼是目前高速串行通訊普遍采用的編碼方式,8B10B編碼的目的是將八位數據轉換成10位的數據,并使轉換后的數據流中“0”和“1”的數量平衡,避免發送過程中因過多重復的出現“0”或“1”而發生的錯誤,提高線路傳輸的性能,有利于接收器更準確的捕捉同步時鐘,而且采用特定的碼元可以使接受端更準確地對準碼元。8B10B編碼可以看成是586B和384B編碼的組合,組合過后有些編碼可能有兩個值,“1”和“0”的差值稱為平衡度,用RD-表示平衡度為+2或0,RD+表示平衡度-2或0。將轉換后的數據按平衡度分為RD-和RD+兩列。設變量DISPIN表示正在轉換的數的平衡度,DISPOUT表示下一個轉換的數的平衡度。初始時設DISPIN與DISPOUT相等,先從RD-中開始轉換,如果轉換后的數“0”和“1”的數量相等,繼續在RD-列中轉換下一個數,如果“0”和“1”的數不等,則轉到RD+列中轉換。同理在RD+列中,如果“0”、“1”個數相等則繼續在RD+中,否則換到RD-中。本文引用地址:http://www.104case.com/article/154036.htm

解碼部分將10位數據的前六位和后四位分別按照5B6B和3B4B的列表解碼即可。

3.2 仿真

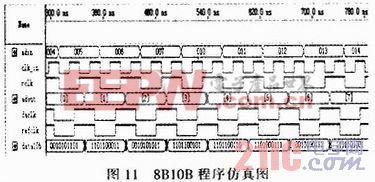

設計程序經QuartusⅡ綜合器編譯綜合成功后,可以對輸入數據、中間產生的數據、輸出數據進行仿真。裝置采用的8B10B編碼方式,分為3B4B和5B6B進行編碼。解碼部分依照編碼時相同的分發將十位數據分為4B和6B分別解碼。解碼后再按順序組合成8位數據。程序以4B3B、6B5B分別查表的方式實現。程序仿真圖中,adin是編碼之前的八位數據,設為逐次加一的計數數據,為了方便比較,圖中用十進制表示。編碼后的十位數據為data10b,adout是解碼后的數據。可以看到雖有延遲,解碼后數據仍為計數數據,因此程序可以準確地實現解碼功能。

4 結束語

綜合以上設計的電路模塊,其基本功能實現了音頻信號的采集與數字化處理,并用光纖完成音頻數字信號的傳輸過程,其信號通道研制完成,為整套實驗裝置的設計研制奠定了基礎保證,它是系統的核心關鍵部分。

作為大學基礎實驗領域研發的新型實驗儀器,不管是設計研制者,還是通過其實驗教學的應用者都在其工作與實驗的實踐中,學習掌握和了解多方面的專業理論與技術知識:1)認識模擬電路、數字電路、模數和數模轉換等電子電路知識,了解印刷電路板設計方法;2)了解可編程邏輯器件的基本原理、硬件設計、軟件編程、仿真調試與使用工作方法;3)了解模擬信號與數字信號的區別與特點,掌握二者之間對應

關系及轉換原理;4)了解音頻信號構成、處理及傳輸過程,以及并/串、串/并轉換的原理及同步工作方法;5)了解光/電和光/電轉換專業知識與當代應用技術;6)學習和了解模擬信號與數字信號光纖傳輸過程等現代電子專業理論與應用技術。

數字通信相關文章:數字通信原理

評論