音頻信號數字化光纖傳輸實驗儀信道的設計與實現

2.3.2 A/D轉換部分

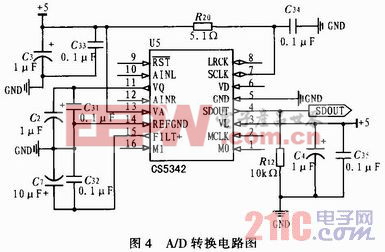

模數轉換電路采用了Cirrus Logic公司出品的專業音頻處理集成芯片CS5342,其工作時鐘頻率設定為18.432 MHz,由FPGA提供。信號由AINL和AINR管腳輸入,SDOUT輸出轉換后的串行二進制數據,LRCK和SCLK輸出采樣頻率。M0和M1腳分別接高、低電平,以保證芯片工作在雙倍速主動模式上,分頻產生采樣頻率96 MHz。另外,RST腳置高電平,各類參考電壓引腳加入適當的濾波電容,使芯片穩定且正確地工作。其電路如圖4所示。本文引用地址:http://www.104case.com/article/154036.htm

2.4 信號發送部分

由FPGA處理后的數據要通過光纖發送,需先將并行數據轉換為串行數據,再將串行數據轉換為光信號。

2.4.1 并/串轉換

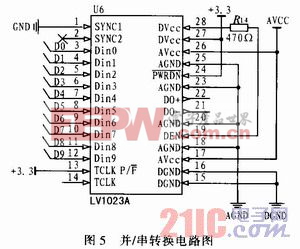

電路采用串化器SN65LV1023A集成芯片實現,電路如圖5所示,其對應接收端由解串器SN65LV1224A集成芯片完成。SN65LV1023A可以將10位并行數據轉換為串行差分數據流,該差分數據流可以由SN65LV1224A還原為10位的并行數據。這一組芯片內部有鎖相環,可以為數據輸出自己匹配時鐘。串化器SN65LV1023A參考時鐘選為18.432MHz與數據在該時鐘頻率下輸入,其芯片內部匹配產生數據輸出時鐘,每一個10位并行數據轉換為12位串行數據,其中多出一個起始位和一個終止位,所以有效頻率為184.32 MHz。解串器的參考時鐘也定為18.432 MHz,以滿足數據傳輸需求。

由于音頻信號是實時不斷的,所產生的數據流連續進行,所以電路不能設置進入高阻態或省電模式,因此LV1023的DEN和PWRDN都置高電位。

串行數據的準確傳輸需要串化器和解串器同步,該組芯片采用的是隨機同步方式。串化器的SYNC1和SYNC2懸空。解串器的LOCK輸入到FP GA以對數據傳輸進行實施控制。

數字通信相關文章:數字通信原理

評論