一種簡易的超寬帶納秒級脈沖發生器設計

2 納秒級脈沖信號的產生

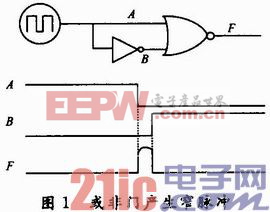

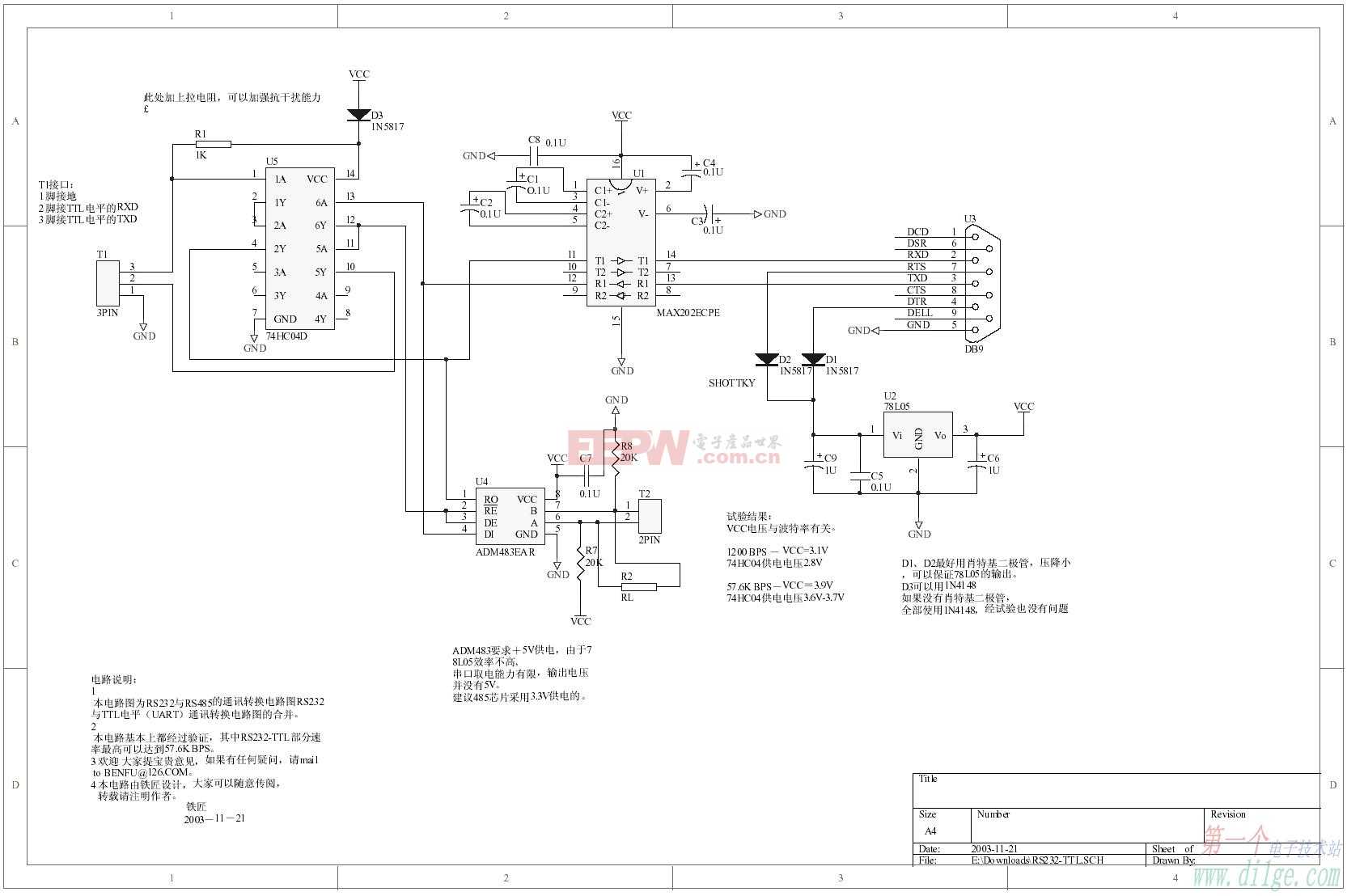

本設計采用數字電路的邏輯特性來產生納秒級窄脈沖信號,然后利用微分濾波產生更適合無線信道傳輸的UWB波形。基于數字邏輯器件產生窄脈沖主要利用的是邏輯門電路的競爭冒險現象來完成。文中采用兩輸入的或非門來產生窄脈沖,如圖1所示。其邏輯表達式為:

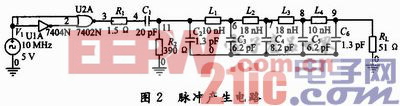

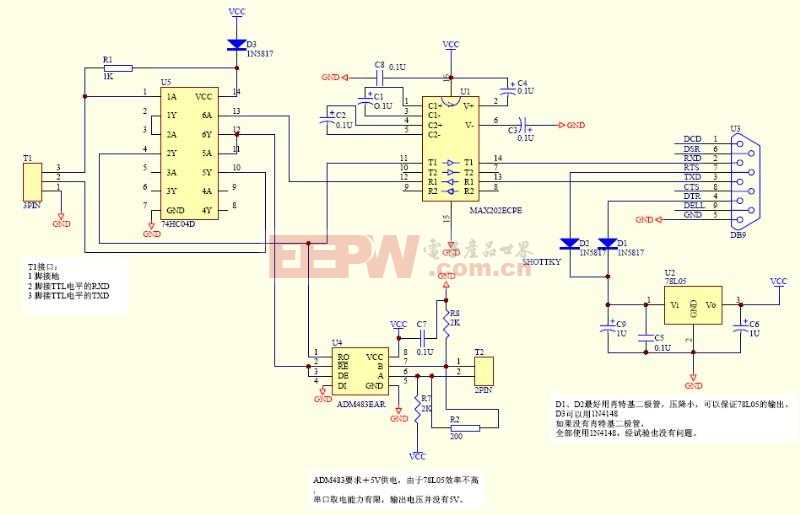

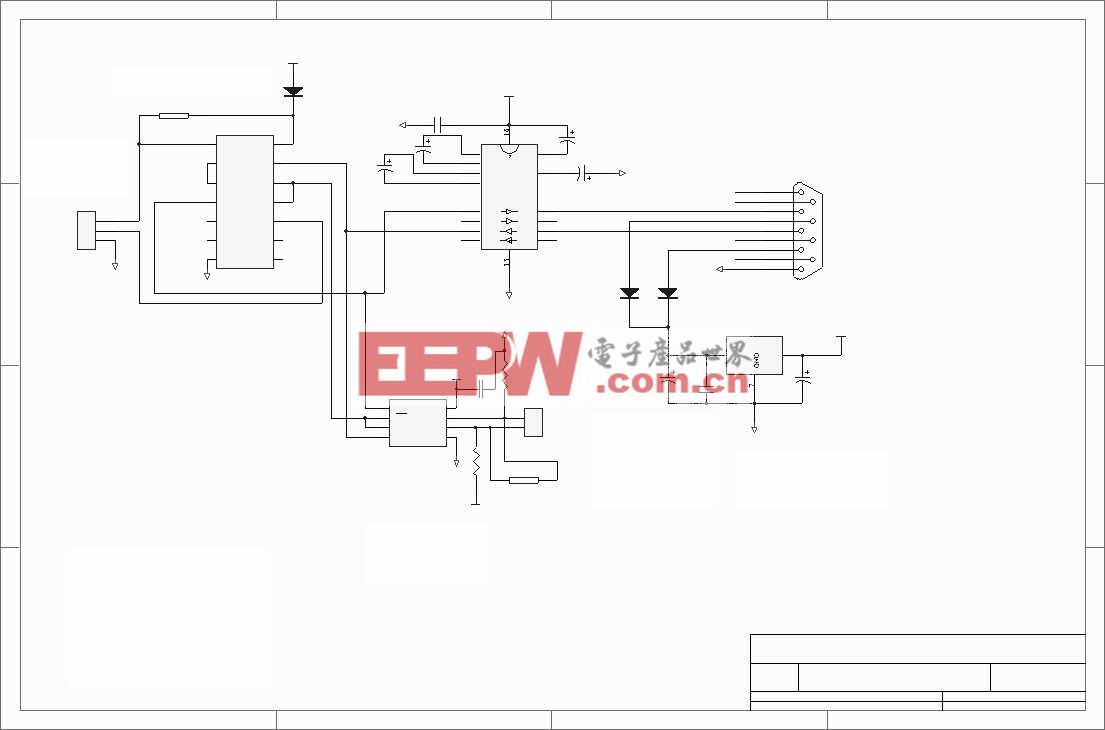

對于TTL器件來說,其產生的窄脈沖近似鐘形,類似于高斯函數波形,通過合理組合RLC元件,就可以產生類似于一階高斯脈沖函數。電路圖如圖2所示。

首先時鐘信號是由10 MHz晶振電路產生,其輸出分別輸入到74HC04和74HC02的一個輸入端。輸入74HC04的時鐘信號經過非門產生一個極性相反、有足夠陡峭的上升沿和幅度的信號,并將其輸入到74HC02的另一個輸入端。由或非門產生一個窄脈沖。后端的微分濾波電路主要完成脈沖的成形,通過調整RLC的參數,就可以得到合理的脈沖波形。其中脈沖延時時間主要由74HC04非門的平均傳輸時延決定,需要注意的是,由于是高速脈沖的傳輸,所以電路的布線也會影響脈沖的延遲時間,所以信號的布線應考慮成傳輸線。

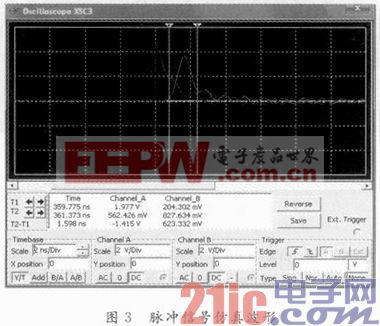

使用Electronics Workbench Multisim 10.O軟件來對電路進行仿真。仿真波形如圖3所示。其結果可得到重復頻率為10 MHz,脈沖幅度為3.59 V,脈沖寬度為1.5 ns的窄脈沖。

評論