基于DDC和DUC的大帶寬DRFM設計與實現

3.2 FPGA中Doppler模塊的實現

多普勒調制原理

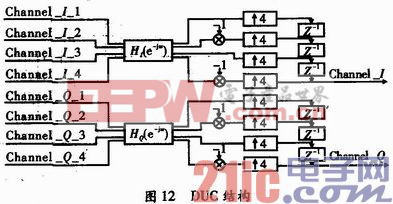

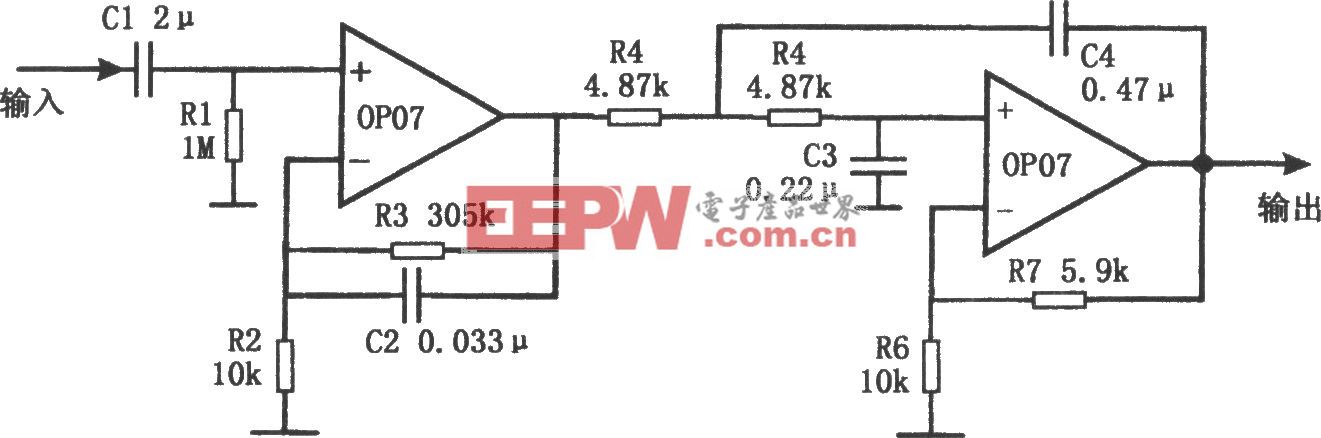

,還原I、Q兩路在時域上的非對齊性,然后各自完成4倍的內插,實現數字上變頻,其結構如圖12所示。本文引用地址:http://www.104case.com/article/153519.htm

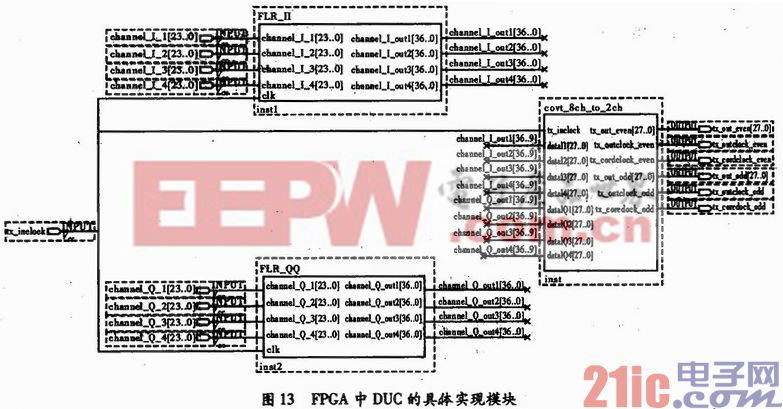

該數字上變頻在FPGA中的具體實現模塊如圖13所示。

3.4 系統在Modelsim中的仿真

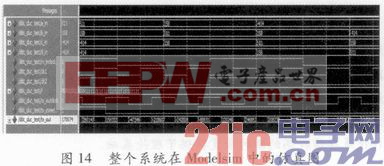

將FPGA中的整個系統在Modelsim中進行仿真,結果如圖14所示。

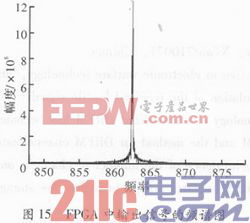

將圖14得到的輸出信號的離散的值導入到Matlab中,查看其頻譜圖,如圖15所示。

如圖15所示,輸出信號頻率為862.5 MHz,與圖5仿真結果相同,由此得出,在FPGA中的整個DRFM系統實現的功能與理論上得到的結果一致,從而完成了DRFM系統的功能,達到了預期的效果。

4 結束語

隨著超寬帶高分辨率雷達在未來戰場發揮的作用越來越大,對于超帶寬雷達的干擾技術研究,將成為雷達對抗領域的重要研究方向。文中針對基于現代化軟件無線電原理的數字下變頻(DDC)和數字上變頻(DUC)技術,對實現的DRFM系統進行了分析及系統仿真,得出的結論與預想結果吻合良好,證明了系統的可行性。

評論