全功能SPI接口的設計與實現

摘要:SPI(Serial Peripheral Interface,串行外圍接口)是Motorola公司提出的外圍接口協議,它采用一個串行、同步、全雙工的通信方式,解決了微處理器和外設之間的串行通信問題,并且可以和多個外設直接通信,具有配置靈活,結構簡單等優點。根據全功能SPI總線的特點,設計的SPI接口可以最大發送和接收16位數據;在主模式和從模式下SPI模塊的時鐘頻率最大可以達到系統時鐘的1/4,并且在主模式下可以提供具有四種不同相位和極性的時鐘供從模塊選擇;可以同時進行發送和接收操作,擁有中斷標志位和溢出中斷標志位。

關鍵詞:全功能SPI;時鐘極性和相位;串行通信;微處理器;中斷控制

SPI串行通信接口是一種常用的標準接口,由于其使用簡單方便且節省系統資源,很多芯片都支持該接口,應用相當廣泛。但是現有文獻和設計多數僅實現了SPI接口的基本發送和接收功能,對SPI接口的時序控制沒有進行深入的研究。全功能SPI接口應具有四種不同的時鐘模式,以適應具有不同時序要求的從控制器。文中主要研究SPI接口的時鐘時序,并用具體電路實現具有4種不同極性和相位的時鐘,最后通過仿真驗證和FPGA驗證。

1 SPI控制器典型結構

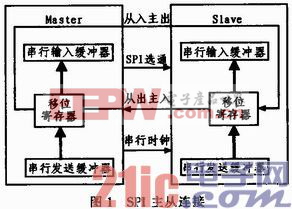

SPI模塊中的典型結構是用于通信的主從2個控制器之間的連接,如圖1所示。由串行時鐘線(SPICLK)、主機輸入從機輸出線(SPISOMI)、主機輸出從機輸入線(SPISIMO)、SPl選通線(SPSTE)4條線組成。當CPU通過譯碼向主控制器寫入要傳輸的數據時,主控制器通過串行時鐘線來啟動數據傳輸,將會在串行時鐘線的一個邊沿將數據移出移位寄存器,而在串行時鐘的另一個邊沿將數據鎖存在移位寄存器中。SPI選通線是SPI控制器的使能端,可以選擇多個從機,實現一主多從的結構,只要SPI選通信號將要選的從機處的選通信號變為低電平就能夠連接成功。

2 全功能SPI控制器設計

2.1 SPI控制器內部結構

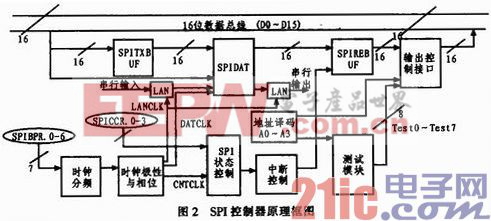

SPI控制器的原理框圖如圖2所示,其中主要包括:

1)SPI控制器的內部寄存器

SPI操作控制寄存器(SPICTL),SPI狀態寄存器(SPISTS),SPI波特率設計寄存器(SPIBRR),SPI接收緩沖寄存器(SPIRXBUF),SPI發送緩沖寄存器(SPITXBUF),SPI串行數據寄存器(SPIDAT),SPI中斷優先級控制寄存器(SPIPRI)。

2)SPI控制器內的功能模塊

時鐘分頻模塊(Frequency Divider),內部時鐘產生電路(Clk_Occur),狀態控制機(Srate Control),中斷控制(IntContro1),測試模塊(Test),輸出控制模塊(Dateout Control)。

2.2 SPI控制器工作原理

圖2給出了SPI控制器的基本原理框圖。SPI控制器可工作在主模式和從模式下,由于在主模式下需要提供相應的時鐘給從控制器,較從模式下工作更為復雜,所以將用工作在主模式下的SPI控制器描述內部工作原理。

在開始傳送數據前,需將SPI控制器進行配置,設定時鐘波特率(SPIBPR),時鐘相位和極性,需要傳送的字符位數(SPICCR)。基本配置結束后,向SPITXBUF和SPIDAT2個寄存器內寫入要傳送的數據時,將會起動一次發送和接收操作。如果有正在傳送的數據,向SPITXBUF內寫入數據,新的數據將在當前數據傳送結束后自動進行發送和接收操作。

評論