基于FPGA的HDB3編解碼器設計

本文在程序的實體中定義了2個輸入端口:時鐘、偽隨機序列,一個兩位的輸出數據(編碼后的輸出)。程序的結構體中使用的是進程語句,共采用4個進程,分別完成判斷4連“0”位置并插入V、記相鄰V碼間1個數、跟蹤V碼位置及編碼輸出的功能。敏感信號均選用的是時鐘信號,對于其任一變化都將同時啟動4個進程,并行執行。在程序中共使用了5個信號,代表了電路的寄存器效果,配置到電路中也相當于寄存器。

3.2 解碼器設計

解碼設計是根據HDB3碼的特點首先檢測出極性破壞點,即找出4連零碼中添加V碼的位置(破壞點位置),其次去掉添加的V碼,最后去掉4連零碼中添加的B碼以將其還原成單極性不歸零碼。

由HDB3碼的編碼規則可知,“0000”都被“000+1”或“000-1”或“+100+1”或“-100-1”取代,所以,只要能檢測出“+1000+1”、“-1000-1”、 “+100+1”、“-100-1”、將它們分別改為“10000” 、“10000”、“0000”、“0000”就可以了。

當然“+1”、“-1”、“0”還是由Data1,Data0來表示,那么就需要有兩個5位移位寄存器(C和D),Data0通過D,Data1通過C。通過D,C來檢測,如果測到兩個移位寄存器分別為“10001”、“0xxx0”或“10001”、“1xxx1”或“1001x”、“1xx1x”或“1001x”、“0xx0x”,數據輸出是將D里面的數據流輸出。所以只要將D中所測到的以上數據分別改為“10000”、“10000”、“0000x”、“0000x”,這樣就可以得到HDB3碼的解碼了。

4 仿真和實驗結果分析

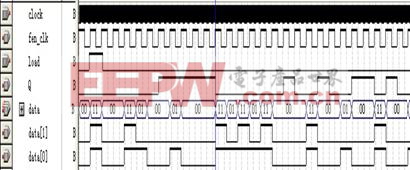

編譯碼器在QuartusII上仿真的波形分別如圖2和圖3所示。圖2中fen_clk為分頻后時鐘信號,load 為使能信號,Q為偽隨機序列,data為編碼輸出。由于輸入的數據流經過了5個寄存器,所以輸出延遲了4個時鐘脈沖周期。但由于時鐘頻率很高,所以影響不大。

圖2編碼器時序仿真波形圖

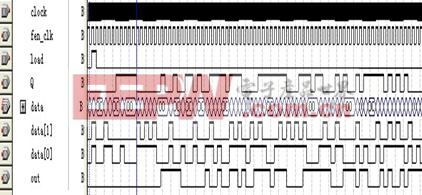

圖3解碼器仿真波形

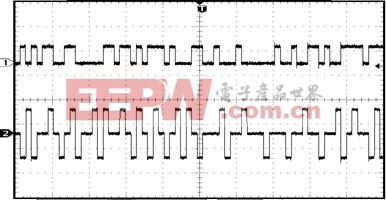

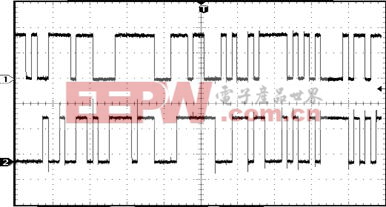

把上述設計下載到Altera EP1C3T144C8芯片上,并通過硬件調試、測試,在示波器上得到偽隨機信號波形、編碼波形和解碼波形分別如圖4和5所示。其中,CH1為偽隨機信號,CH2分別為編碼和解碼信號。測試結果和時序仿真結果無失真。隨機信號輸入相對編碼信號輸出延遲了5個單位時鐘。解碼信號延時了11個單位時鐘。

圖2編碼器時序仿真波形圖

圖5 偽隨機信號和解碼信號波形

5 結論

實踐表明,運用FPGA來實現NRZ碼到HDB3碼的轉換與采用專用集成電路CD22103相比,不僅給調試帶來了方便,而且可以把編碼電路和解碼電路及其它電路集成在同一塊FPGA芯片中,減少了外接元件,提高了集成度。該設計已成功應用于網絡化集中照明控制系統中。

評論