一種新型多DSP并行處理結構

簇內存在一個瓶頸,這是因為在每個周期里只有兩個處理器可以通過共享的總線進行通信,其它的處理器則被阻塞,直到總線被釋放為止。由于ADSP-21161N也可以在一個簇中進行點對點的鏈路口傳送,該瓶頸很容易被消除。通過普通總線可以動態的建立和激活處理器間的數據鏈接。由于ADSP-21161N僅有兩個鏈路口,各處理器間只能兩兩相連構成一條鏈路,不相鄰的兩個處理器節點之間的通信則要通過中間節點給予支持。但由于ADSP-21161N的鏈路口數據傳輸速率為100MB/s,而且傳輸字寬為8bit,基本可以消除此瓶頸的影響。

2.3 多處理器總線仲裁

多個ADSP-21161N可以共享外部總線,而不需要另外的仲裁電路。間進行仲裁,和主機處理器之間的總線控制權傳遞。總線仲裁可以采用兩種不同的優先權機制解決總線請求的競爭:固定優先權和循環優先權。RPBA管腳決定使用哪種優先權機制。當RPBA為高電平時選擇循環優先;當RPBA為低電平時選擇固定優先。由于循環優先機制控制比較復雜,因此一般可用固定優先機制,經過實踐檢驗,固定優先機制很容易用,而且效果不錯。在固定優先機制中,參與競爭總線的ADSP-2116IN中,ID號最小的ADSP-21161N將成為主處理器,從而可以將優先級較高的處理工作放在ID號較小的處理器中。在軟件優先權控制上則需要較少的運算開銷。

要連在一起,21161N的數量。每個處理器驅動與自身ID2-0輸入相如果系統中的ADSP-21161N少于6片,應上拉為高電平。

ADSP-21161N具有設計多處理器系統的功能,包括總線控制仲裁、對其它ADSP-21161N的內部存儲器和IOP寄存器的訪問等。在多個ADSP-21161N共享總線式多處理機系統中,任何一個處理器都可以成為總線控制者。

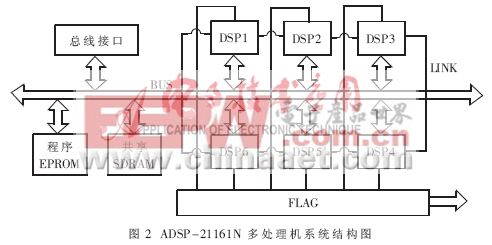

實現一個典型的多DSP并行處理結構,各處理器的三大總線要全部相連。圖2給出了一個基本的多處理器系統結構圖。在多處理器系統中,某一時刻總線由主處理器控制,并且主處理器驅動所有總線。由于配置成多處理器后,包括片內存儲器以及IOP寄存器在內的所有地址空間是統一編址的,因此事實上只有兩個節點(處理器或外設)在同一時刻在總線上活動,而此刻總線對于其它節點來說是阻塞的。這樣,其它接點只能通過鏈路口或者FLAG標志口進行點對點通信來交換數據和消息。

在多處理器系統中,各控制線上除主DSP外的其它所有節點都屬于負載,所以對于每一根控制線來說都是一個多負載的連接,必須在每個DSP附近接串接電阻以增強驅動能力,否則會由于驅動能力不足而導致所進行的操作失效。另外在所有低電平有效的控制線上應接上拉電阻,以保證在沒有進行操作時從DSP以及外設不會接收到虛假的指令。由于本系統是一個獨立的結構,并沒有與外部主機相連,故主機接口控制線在各DSP相連的情況下,應像其它未用管腳一樣根據ADI技術文檔的要求進行處理。而本結構與外部的通信可以通過同步串口或者在總線上掛接一片雙端口RAM來進行。

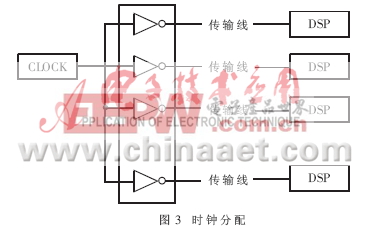

另外多處理器系統的時鐘、復位同步問題是一個決定系統工作正常與否的關鍵問題,各DSP的復位信號可同時接到看門狗的輸出端。時鐘信號必須在阻抗可控的傳輸線中傳輸,為保證各DSP的時鐘信號之間不存在相位差,或者說相位差在系統允許的范圍內,一般應采取始端連接的方式。圖3給出了串聯傳輸線分配時鐘的例子,它允許在不同的路徑中存在延時,每個設備必須在線的終端。傳輸路徑必須均勻分布,以使各路徑上的傳輸延遲相互匹配。匹配的反相器必須在同一IC上,且相互之間的時間滯后差必須小于1ns。

并行處理系統的硬件結構搭建好后,如何才能很好地發揮其超強的處理能力,則要靠軟件的設計來實現。為適應計算任務的多樣性,可以采用1片ADSP-21161N作任務管理器,另外5片ADSP-21161N作運算器的主、從式拓撲結構。這樣做還有利于實現指令間的流水處理,提高執行效率。而軟件實現則可以根據具體的要求來完成,考慮到系統的高速、高效、實時性,軟件可采用ADSP-21161N匯編語言進行編程。

本文以通用高速實時信號處理系統的設計為應用背景,提出了一種由6片ADSP-21161N構成的并行處理結構。它充分利用ADSP-21161N芯片本身支持多處理器并行運算的特點構成了簇式多處理器結構,并輔以鏈路口互聯的點到點通信、FLAG標志互連的消息傳遞等靈活多樣的通信方式,具有運算能力強、I/O帶寬寬、通信手段方便多樣、能靈活地改變拓撲結構、可擴展、通用性強等特點。以此并行處理結構為核心輔之高速數據采集系統,并用高速FPGA作為系統控制設計實現了通用高速實時信號處理系統。實驗表明,這種并行計算結構易于控制,工作效率高,并且穩定可靠。

評論