安全認證系統中嵌入USB接口技術

USB(Universal Serial Bus)通用串行總線是計算機與其外圍設備通信的一種總線標準,是近年來應用在PC領域的新型接口技術。它的熱拔插、即插即用、連接簡單、高帶寬、可總線供電等優點幾乎使其成為目前計算機外設的首選通信接口。世界上幾乎所有硬件廠商都生產實現USB協議的芯片。廠商們本著通用性原則,有的在芯片中嵌入了通用微處理器,如CYPRESS公司CY7C6××××系列和INTEL930××系列嵌入了8051系列微控制器;有的則提供了各種常用的與微處理器接口的方案,如NATIONAL SEMICONDUCTOR公司的USBN960× 系列提供了多路與非多路的8位并行接口、DMA并行接口及微波接口;PHILIPS公司的PDIUSBD11提供了I2C總線接口;三星公司研制的USB功能控制器則具有8位并行微處理器接口,并能以同步或者異步方式工作,這為使用USB協議作為通信接口提供了極大的方便。然而,將USB功能嵌入到一種用于安全認證的處理系統中,則存在無法與處理器直接接口的問題。本文探討了USB功能模塊和處理器接口技術,并從其基本應用角度出發,給出了相應的軟件流程。具有USB接口的安全認證系統使用簡單、便于攜帶、通信速度快。

本文引用地址:http://www.104case.com/article/152564.htm1 USB功能模塊

USB功能模塊是基于微處理器應用實現USB協議的模塊。集成有低速USB收發器,配置有3個基于FIFO的端點、1個控制端點(8字節)、2個可配置傳輸方向的中斷端點(8字節)。每個端點都配置有相應的控制與狀態寄存器,帶有一個8 位微處理器并行接口,可工作在同步或異步方式。

USB功能模塊的操作對用戶來說是完全透明的。包的譯碼、數據傳輸到FIFO、從FIFO發送數據和USB包的裝配都是自動完成的。當接收到一個正確數據包或發送成功一個數據包,即向MCU發出中斷請求,請求將數據取走或裝入下一個要發送的數據包。端點FIFO對USB來說是緩存單元,對MCU來說是一個I/O端口。微處理器通過訪問USB寄存器來控制USB模塊的操作。

1.1 端點0控制/狀態寄存器

D0:OUT_PKT_RDY FIFO裝有一個有效數據包,USB將其置1,產生中斷,MCU寫D6為1,清除D0。

D1:IN_PKY_RDY USB成功發送完一個數據包,清D1時產生中斷。

D2:SENT_STALL 控制交換因違反協議而終止,USB置D2,產生中斷。

D3:DATA_END MCU裝了最后一個數據包到FIFO,置D3,與此同時,置D1。MCU卸載完FIFO最后一個數據包,清D0,置D3。對于0長度的數據相,MCU卸載完SETUP數據包之后,清D0=0,置 D3=1。USB清D3時產生中斷。

D4:SETUP_END 在DATA_END(D3)置位之前,控制傳輸結束,USB置D4,產生中斷。

D5:SEND_STALL 如果譯碼為一個無效的令牌,MCU置D5,與此同時,清D0,USB發STALL給當前的控制傳輸,MCU寫D5=0,結束STALL條件。

D6:SERVICED_OUT_PKY_RDY MCU寫D6=1以清除D0。

D7:SERVICED_SETUP_END MCU寫D7=1以清除D4。

1.2 USB功能模塊的訪問時序

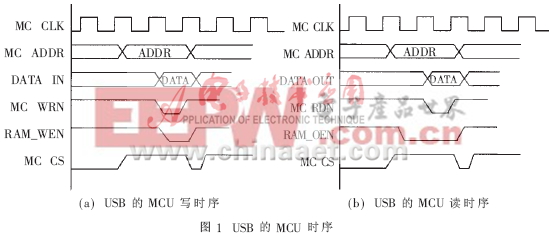

USB功能模塊的I/O接口可工作在同步或異步方式,本文采用同步方式。其對MCU訪問的讀寫時序要求如圖1(a)、(b)所示。

寫時序:地址至少要維持兩個時鐘周期,并且要先于數據一個有效時鐘周期,以便將FIFO的寫指針選通至RAM寫地址端口。當寫信號有效時,存儲器寫使能信號有效,寫之后一個時鐘周期FIFO指針刷新。地址有效時,片選高有效。

讀時序:一旦地址有效,存儲器輸出使能有效。地址至少維持兩個時鐘周期,前一個周期將FIFO的讀指針選通至RAM的讀地址端口,因此數據比地址晚一個時鐘周期出現在數據總線上。當讀信號有效時,MCU將總線上的數據讀走,與此同時,FIFO的指針刷新。地址有效時,片選高有效。

系統中采用了具有加解密功能的處理器。處理器采用棧式結構,具有焦點聚合的低功耗內總線結構和超標量指令結構與多種尋址方式等特點,能高速高效地處理數據。嵌入有RSA和DES模塊,能對發送和接收的數據進行實時RSA算法或三重DES算法的加密和解密。系統具有8位地址總線,16位數據位寬的并行接口,其I/O訪問時序如圖2所示。從圖2可以看出,I/O訪問在一個時鐘周期內完成。

評論