大容量SDRAM在windows CE系統中的應用設計

2.2.2 數據線、地址線的分配

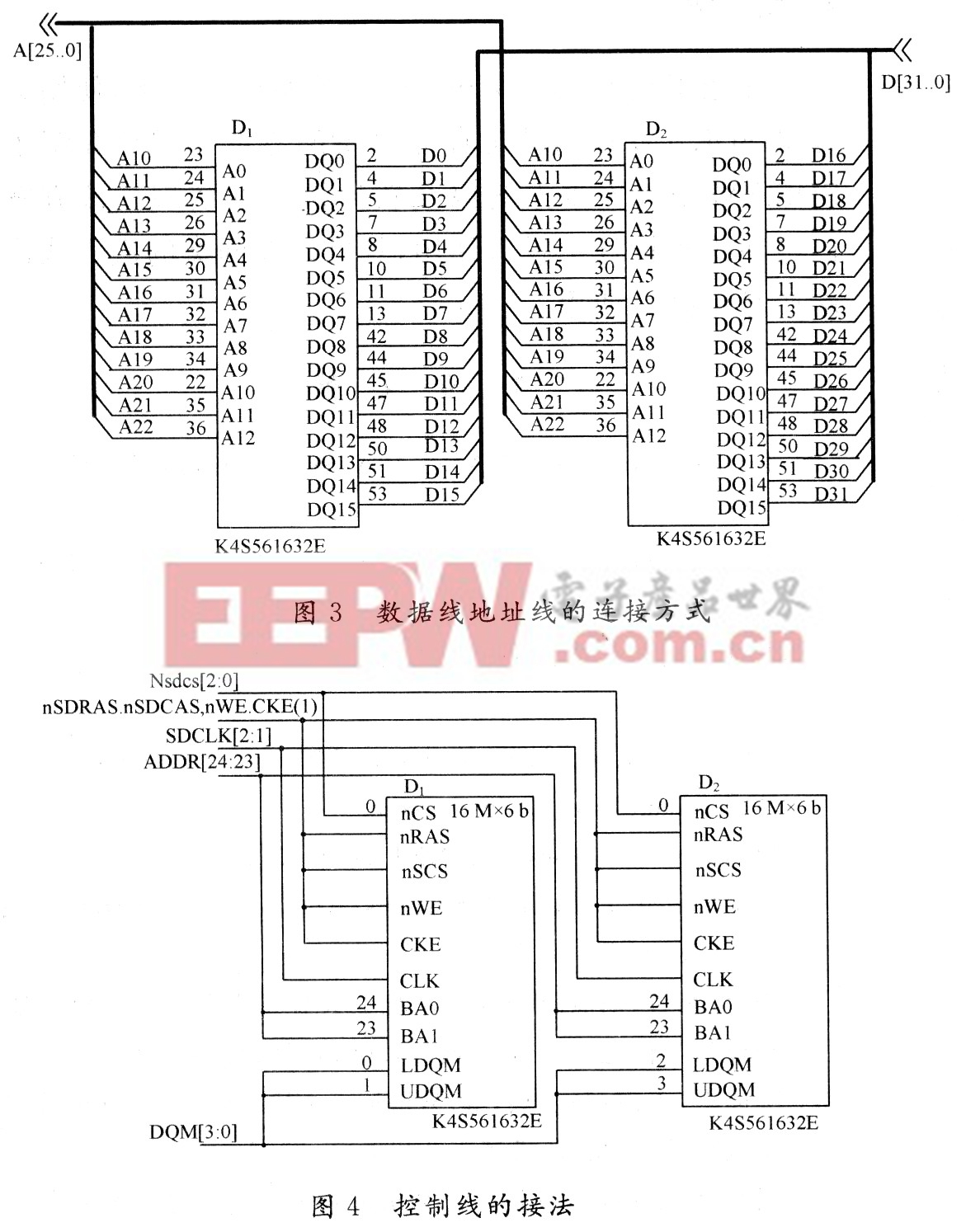

PXA255處理器共有32位數據線和26位地址線。故在硬件設計時需要并行處理2塊16 b的SDRAM,分別連接高位和低位的16根數據線。

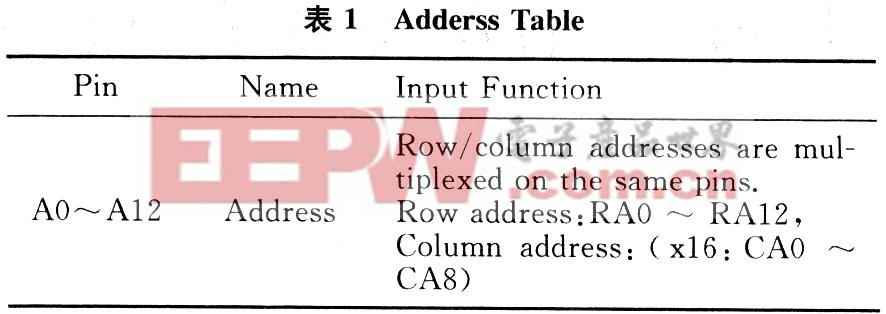

對于地址線的連接,首先需要參考SDRAM的數據手冊,確定SDRAM行列地址線的個數。其次根據處理器數據手冊確定具體地址線的連接方式。

在三星K4S561632E的數據手冊中是這樣給出的,如表1所示。本文引用地址:http://www.104case.com/article/152475.htm

從表1中可以得出行列復用13根地址線,其中行地址13根,列地址9根,共組成22根地址線的尋址空間。在處理器PXA255中,給SDRAM分配的地址線空間是從A10~A22。這樣就可以完全確定地址線和數據線的連接方式,如圖3所示。

2.2.3 控制信號線的連接方式

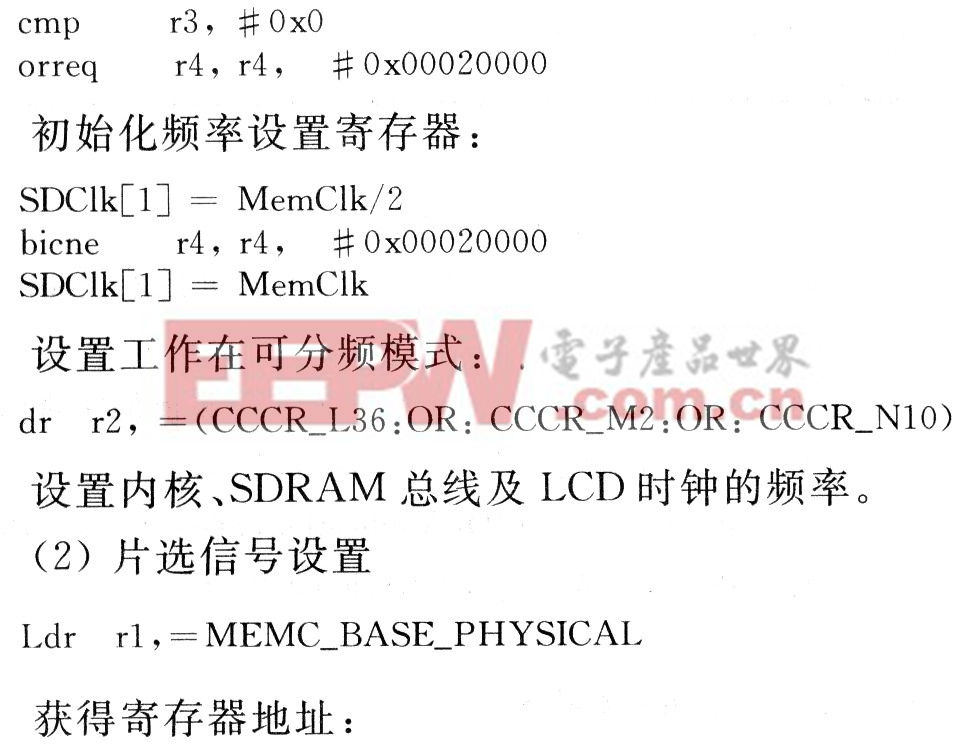

對于SDRAM需要確定的控制線包括時鐘信號線、區域片選信號線及Bank片選信號線。對于這三類信號線PXA255處理器是這樣給出的,即:

(1)每兩組內存區域使用同一組時鐘信號線,即每128 MB的內存空間使用同一根時鐘信號線,故在設計中使用了2組時鐘信號線。

(2)共有4根區域片選信號,分別控制64 MB的物理地址空間。最大支持到256 MB的物理地址空間。

(3)地址線的23,24位用來實現對SDRAM內部Bank的選擇。

2.3 硬件的移植

針對于PXA27x系列的高端處理器,Intel并沒有對SDRAM部分做本質上的改動,仍然是4根動態片選信號,故硬件方面的設計可以完全移植到PXA27x系列的處理器中。

3 軟件設計方案

Windows CE操作系統下對內存的驅動代碼主要分為兩個部分,首先在BootLoader中對SDRAM進行底層初始化;其次在系統BSP包內需要將SDRAM所對應的物理地址映射為Windows CE下能夠識別的虛擬地址。

控制線的連接方式如圖4所示。

3.1 BootLoader代碼的買現

BootLoader是系統運行的起始點,它包含著系統運行的第一行代碼。BootLoader本身也是一個功能完整的微型操作系統,在內部需要實現任務調度、內存管理、文件系統,以及各種必要設備驅動程序的配置。其中內存管理即是完成SDRAM初始化的工作,包括設置SDRAM工作頻率、設置片選信號寄存器、設置刷新間隔和SDRAM潛伏期、以及配置系統內核的拷貝地址。控制線的連接方式如圖4所示。

(1)頻率設置

完成寄存器的復值,其中r3的選擇為F即就是0x1111,打開4片內存區域。

評論