Chirp函數(shù)的Nios Ⅱ嵌入式實現(xiàn)

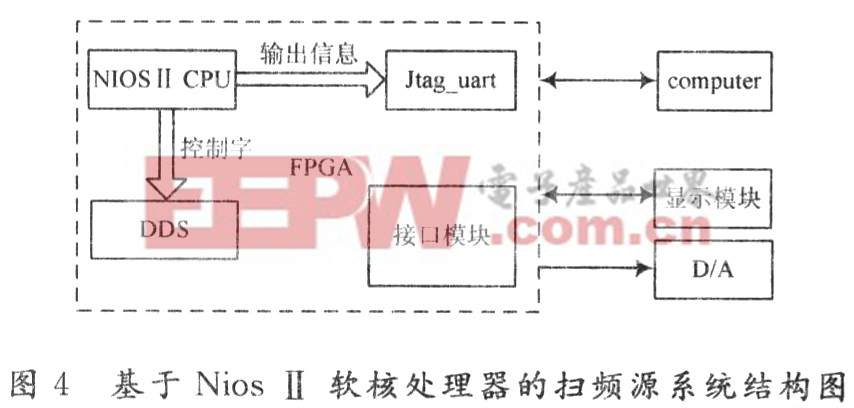

因此該Chirp信號源的功能是:在NiosⅡ中建立的微控制器;使用嵌入式操作系統(tǒng)μC/OS-Ⅱ建立對DDS頻率控制字輸出實時改變的任務(wù);根據(jù)線性和非線性Chirp函數(shù)的特點控制字的輸出根據(jù)需要線性或者非線性輸出,并且在此設(shè)計中將該任務(wù)的優(yōu)先級設(shè)置為最高。利用VHDL語言編寫DDS模塊,首先根據(jù)Matlab計算出需要的正弦數(shù)據(jù),然后將這些數(shù)據(jù)存儲于ROM中供DDS模塊調(diào)用,并且通過微控制器中的Jtag_uart傳輸模塊在編程監(jiān)視窗口實時觀測當(dāng)前輸入頻率的大小,具體結(jié)構(gòu)如圖4所示。本文引用地址:http://www.104case.com/article/152464.htm

2 DDS模塊的設(shè)計

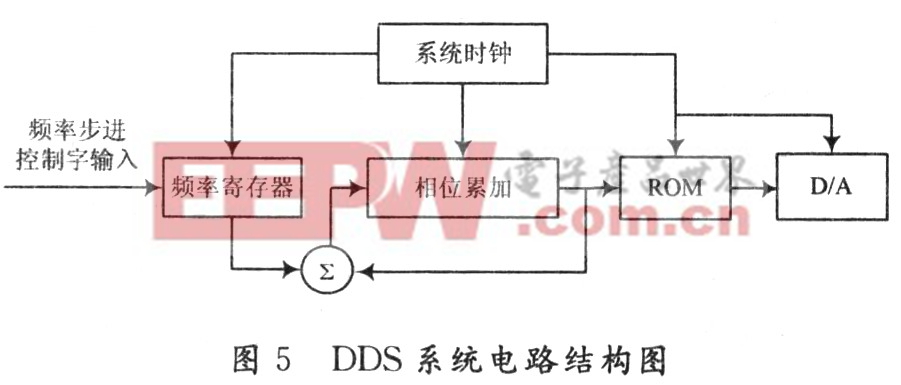

數(shù)字式頻率合成器(DDS)模塊的工作原理是:將O~2π的正弦函數(shù)值分為N份,將各點的幅度值存入ROM中,再用一個相位累加器每次累加相位值ωT,得到當(dāng)前的相位值,通過查找ROM得到當(dāng)前的幅度值。其系統(tǒng)框如圖5所示。

DDS的幾個主要參數(shù)是:系統(tǒng)時鐘頻率,頻率控制字長,頻率分辨率,ROM單元數(shù),ROM字長。該設(shè)計的DDS是32位的,時鐘頻率為50 MHz,頻率控制字長為32位,ROM單元數(shù)為2的11次方,ROM字長為16位。而且有如下關(guān)系:

頻率分辨率=系統(tǒng)時鐘頻率/232;

頻率控制字(FTW)=f×232/T;

其中:f為要合成的頻率;T為系統(tǒng)時鐘。

DDS的工作過程為:每次時鐘的上升沿到來時,相位累加器(32位)中的值累加上頻率寄存器(32位)中的值,再利用累加器的高11位作為地址進行ROM查表,輸出相應(yīng)的幅值數(shù)字信號。

如果是掃頻工作,只需要根據(jù)一定的規(guī)律實時修改頻率控制字,就可以達到掃頻輸出的目的。但是該系統(tǒng)的性能受到以下兩個方面的制約:ROM單元數(shù)和ROM數(shù)值的有限字長。由于ROM大小的限制,ROM的單元地址位數(shù)一般都遠小于相位累加器的位數(shù),這樣只能取相位累加器的高位作為ROM的地址進行查詢,這就相當(dāng)于引入了一個相位誤差。而且ROM的有限字長,不能精確表示幅度值,相當(dāng)于引入了一個量化誤差。因此應(yīng)根據(jù)系統(tǒng)的性能要求選擇合理的ROM。為了解決ROM的受限問題,該設(shè)計采用ROM壓縮技術(shù)。因為正弦函數(shù)存在對稱和反轉(zhuǎn)特性,即:

對于O~2兀的幅度值,可以只存儲O~π/2的部分。這樣原本需要的2的11次方個單元的ROM現(xiàn)在只需要2的9次方個單元的ROM就可以實現(xiàn)。在MatIab中產(chǎn)生16位512點的O~π/2正弦波數(shù)據(jù)的命令如下:

![]()

將Y數(shù)據(jù)依次存入Altera公司提供的Megawiz-ard宏單元實現(xiàn)的ROM中即可。

3 嵌入式微處理器的實現(xiàn)

嵌入式微處理器的設(shè)計包括3個部分:利用SoPCBuilder定制的軟核CPU,在QuartusⅡ環(huán)境下設(shè)計的電路和NiosⅡ編程。

本設(shè)計的軟核CPU采用NiosⅡ/S標準型內(nèi)核,帶有16 KB的Cache;集成了外部的FLASH和SDRAM控制器用于保存程序數(shù)據(jù);Jtag_Hart電腦開發(fā)板傳輸接口用于建立良好的用戶交互接口使用戶能在console界面上觀察程序運行情況;兩個位寬分別為8位和3位的輸出口作為輸出DDS模塊的控制字;定時器用于產(chǎn)生CPU系統(tǒng)時鐘;LCD控制接口用于在LCD顯示一些需要的信息。

評論