嵌入式實時圖像處理系統(tǒng)中SDRAM控制器的實現(xiàn)

對該主控制器有以下兩點需要說明:

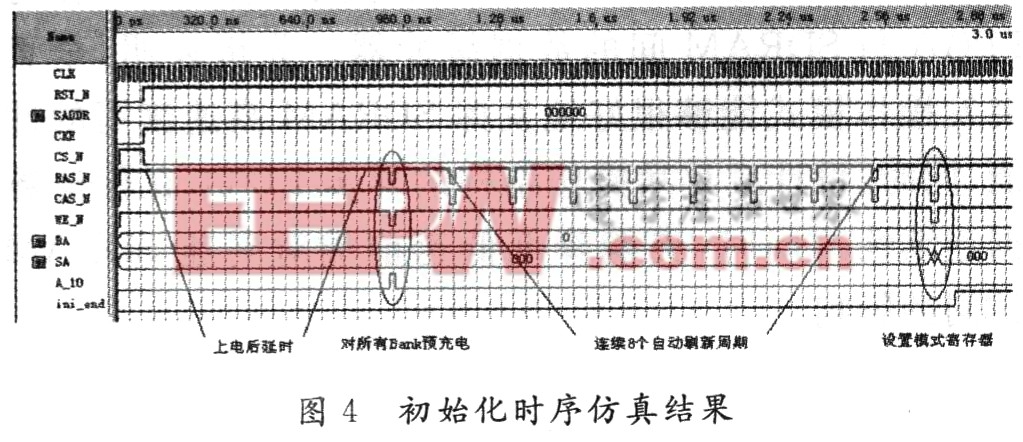

(1)器件僅在上電后進行一次初始化配置,進入正常工作狀態(tài)后就不再改變工作模式。初始化時序仿真結(jié)果,如圖4所示。

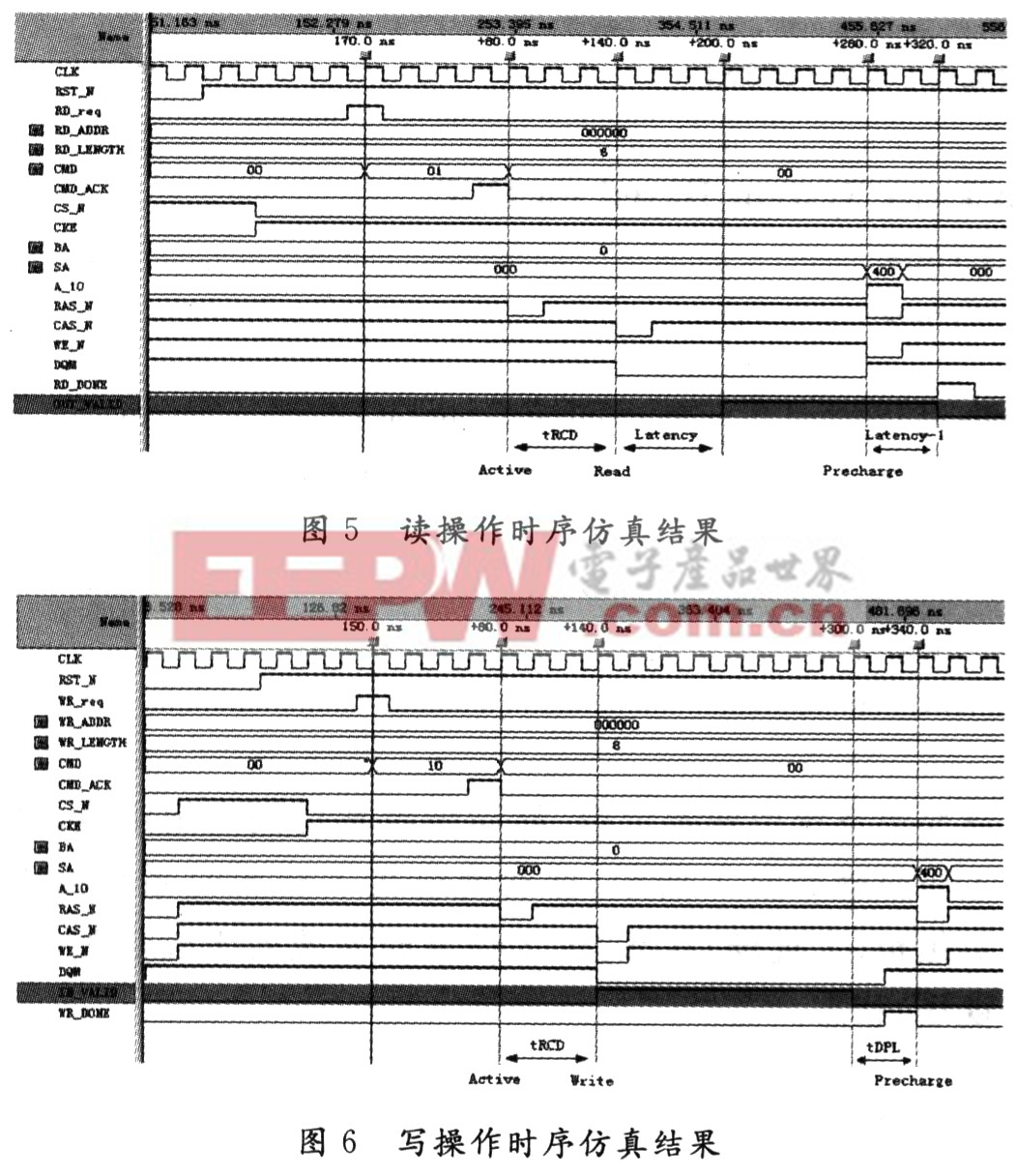

(2)當SDRAM工作在全頁突發(fā)模式時,讀寫操作所訪問的地址將在頁內(nèi)循環(huán),直至收到Burst-Termi-nate命令或Pre-charge命令。由于在Burst-Termi-nate命令后還需發(fā)出Pre-charge命令,才能保證芯片正常工作,因此設(shè)計采用了Pre-charge命令終止頁模式。為保證LENGTH數(shù)據(jù)中正確讀出或?qū)懭?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/SDRAM">SDRAM,發(fā)出Pre-charge命令時必須滿足一定的時序要求。對于讀操作,Pre-charge應(yīng)在最后一個有效輸出數(shù)據(jù)之前CL-l時鐘發(fā)出;對于寫操作,Pre-charge應(yīng)在最后一個有效輸入數(shù)據(jù)之后tDPL時間發(fā)出。圖5和圖6給出SDRAM控制器的讀寫操作時序仿真結(jié)果,其中,OUT_VALID及IN_VALID信號分別表明輸出及輸入數(shù)據(jù)有效。

3 結(jié) 語

針對實時圖像處理系統(tǒng)的特點,定制SDRAM控制器。在Altera公司的主流芯片Cyclone II(EP2C70F896C6)上成功地使用了Verilog HDL編程語言,其占用355個邏輯單元(不到FPGA總邏輯資源的1%);4個M4K塊和1個PLL鎖相環(huán)。在320×240的實時紅外熱成像系統(tǒng)中,該SDRAM控制器的工作狀態(tài)良好,并可通過改變LENGTH參數(shù)而方便地用于任意分辨率的實時圖像處理系統(tǒng)中,可移植性強。

評論