基于DSP的高性能通用并行彈載計算機設計與實現

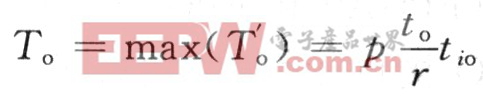

首先考慮共享總線結構。設

![]()

假設任務均勻分成p部分,就有:Te=pt。在最壞情況下,p個處理器總是同時訪問總線,考慮最后得到總線訪問權的處理器:

Tp是每個處理器上并行算法運行時間,在最壞情況下,Tp=Te+To。設問題規模W為最佳串行算法完成的計算量,即W=Te,加速度比:

顯而易見,共享總線系統的并行效率隨著處理器數目p的增大而下降。

而在分布式并行系統中,理想情況下任一時刻都可有兩個處理器通過其通信口相互交換數據,設一個通信口傳送一個數據的相對時間為tcomm,等效為處理器運算能力和通信口傳輸能力之比。同時,假設每次交換還需對本地存儲器訪問。這樣就有通信開銷:

和處理規模p成線性關系,并行效率與p無關。

以上討論的是假設任意兩個處理器之間可以直接進行數據交換,而在實際情況下,尤其是處理器數目p多于處理器的通信口數量時,兩個非直接相連的處理器之間的數據交換所需開銷與其經過的路徑成正比關系。但這并不影響以上討論的公式。因為在規則網絡拓撲結構中最大或平均路徑是一個定值n,那么這時,分布式并行系統的加速比公式為:

可見,在這種情況下分布式并行系統同樣能獲得線性加速比。由以上理論分析可知,共享總線并行結構適合共享存儲編程模型,進行細粒度的并行處理,但其擴展性能較差,處理器的數目有限,單機處理性能有限;分布式并行結構采用消息傳遞的機制,適合進行粗粒度的并行處理,便于大規模的系統擴展,提供強大的整體性能。

2 彈載計算機的設計實現

由于彈上信號處理算法的復雜性,信號處理系統具有復雜多樣的并行處理模式,如基于空間的數據并行處理、基于時間的流水并行處理等。另外,彈上計算機系統具有多種類型的數據流,如原始數據流(A/D采集之后的數據流)、中間數據流(各處理節點之間傳遞的數據流)、定時同步信號以及控制數據流等。這些不同的數據流的傳輸帶寬不同,因此系統中要有與這些不同數據流相匹配的互聯網絡。

高性能通用并行彈載計算機是構建信號處理系統的基礎。它除了選用高性能的處理器外,為了具有通用性,還要具有標準化、模塊化、可擴展、可重構的特點,以便構建各類控制和信號處理系統。同時為了適應控制和信號處理系統復雜并行處理模式和多種數據流的特點,它要具有混合的并行模式和多層次的互聯網絡。基于這些要求和上文中對并行處理結構模型的理論分析,筆者選用當前業界最高性能的浮點DSP芯片TS201和大規模FPGA,設計了一個標準化、模塊化、可擴展、可重構、混合并行模式、多層次互聯的高性能通用并行彈載計算機。圖2是其結構框圖。

評論