基于DSP的高性能通用并行彈載計算機設計與實現

摘要:為滿足彈上信號處理領域不斷增長的任務需求并適應不同的應用場合,設計高性能通用并行計算機,進而構建各類信號處理系統是一種趨勢。基于時共享總線和分布式兩種并行結構的理論分析,結合信號處理系統的特點,設計了一種高性能通用并行彈載計算機,它具有標準化、模塊化、可擴展、可重構、混合并行模式、多層次互聯的特性,通過構建典型彈載計算機驗證了這些特性。

關鍵詞:彈載計算機;并行處理;TS201;FPGA

0 引 言

隨著技術的發展,在導彈控制和通信等領域,需要處理的任務規模越來越大。雖然隨著VLSI技術的發展,已產生了運算能力達每秒幾十億次的處理器,但還遠遠不能滿足這些領域的需求。而VLSI技術的發展已受到其開關速度的限制,進一步提高處理器主頻遇到的困難越來越大。為此,把用于大型計算機的并行處理技術應用到信號處理中來,在信號處理系統中引入并行多處理器技術是必然趨勢。傳統彈載計算機一般針對特定場合,先確定算法,再根據算法確定系統結構,由于系統結構與算法嚴格相關,因此通用性較差。隨著一些標準技術(標準板型、接口、互聯協議等)在彈上控制系統中的應用,設計標準化、模塊化的通用型計算機成為了可行。而且所設計的還要可擴展、可重構,進而根據不同的應用場合和算法構建各種彈載計算機系統。

1 并行彈載計算機處理結構模型

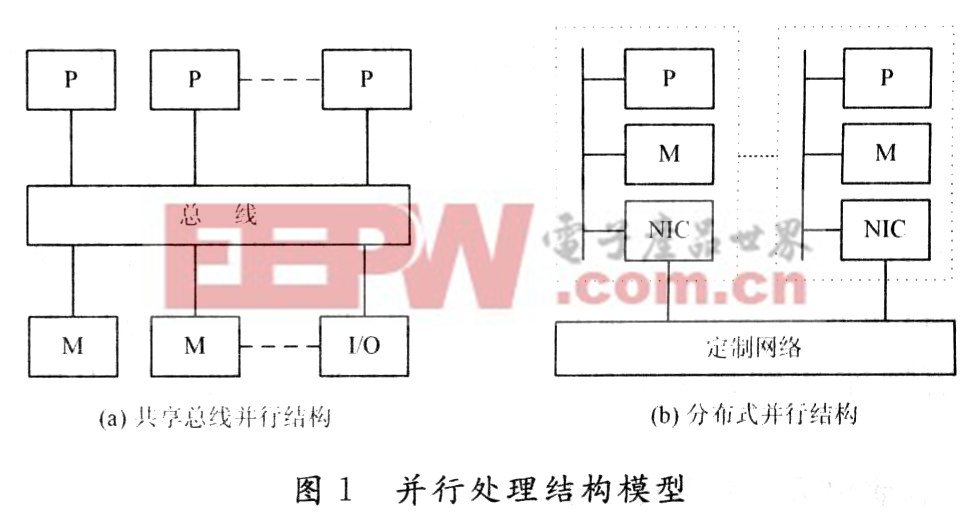

普遍的兩種并行處理結構如圖1所示,一種是共享總線結構,另一種是分布式并行結構。其中,P(Proces-sor):處理器;M(Memory):存儲器;MB(Memory Bus):存儲器總線;NIC(Network Interface Circuitry):網絡接口電路。共享總線結構中多個處理器P經由高速總線連向共享存儲器,每個處理器等同地訪問共享存儲器、I/O設備和操作系統服務。分布式并行結構中多個處理節點通過高通信帶寬、低延遲的定制網絡互聯,每個處理節點都有物理上的分布存儲器,節點間通過消息傳遞相互作用。

并行處理的目的是采用多個處理器同時對任務處理,從而減小任務執行時間,它主要反映在加速比(S)和并行效率(E)上。加速比是指對于一個特定應用,并行算法的執行速度相對串行算法加快了很多倍。效率則是針對每個處理器來衡量的。依據并行處理中可擴放性(Sealability)評測的等效率度量標準可從理論上評測這兩種結構。

評論