多對一嵌入式稅務控制器研究初探

4.3 使用雙處理器嵌入式稅務控制器實現“多對一”:

該方法不需在軟件設計上增加并行計算,原有的稅控軟件可直接移植到嵌入式稅務控制器中即可使用。該嵌入式稅務控制器采用雙處理器,共享內存,其它如嵌入式的IO、網卡、稅控芯片及閃存 flash的連接與單處理器相同。此時控制器的算法依然采用多線程技術,只是由于現在增加了處理器的數量,線程的調度、運行效率將大大提高。

5 多對一嵌入式稅務控制器的硬件設計實現:

我們采用 FPGA技術進行多對一嵌入式稅務控制器設計。

FPGA(Field Programmable Gate Array,即現場可編程門陣列),可提供高性能的數據和控制處理功能,具有規模大、可重復編程、開發投資小等優點,在現代電子產品中應用得越來越廣。因此,利用 FPGA技術實現多對一嵌入式稅務控制器是較好的設計方案。

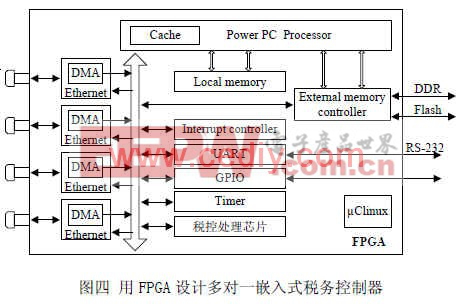

在本文,使用Xilinx 的 VirtexO-4 FX進行設計,VirtexO-4 FX內建 PowerPC雙處理器,能對數據進行高速并行處理,效能提升很大。VirtexO-4 FX FPGA包含高性能的可編程架構、嵌入式 PowerPC處理器和 3.125Gbps收發器,從而成為嵌入式稅務控制器的理想選擇。實現方案如圖四所示。

本文引用地址:http://www.104case.com/article/152383.htm

6 結束語

采用多對一嵌入式稅務控制器是降低商家稅控系統采購成本,進而順利推進商業稅控自動化的非常重要的技術環節。在本文,分析了無線、有線兩種連接嵌入式稅務控制器的組成形式,提出了用并行架構及雙處理器來實現多對一嵌入式稅務控制器的設計思想,提出了多對一嵌入式稅務控制器硬件實現的基本方法,即 FPGA方法。用并行架構和采用集線嵌入式稅務控制器及多線程技術實現多對一是本文的創新點,它為更好地提高現有嵌入式稅務控制器的處理效率、減少商場采購壓力、和在現有條件下實現更先進的稅務控制等方面提供了更深層次的設計思路和解決辦法。

pos機相關文章:pos機原理

評論