基于CPLD譯碼的DSP二次Bootloader方法

二次Bootloader的原理是由用戶自行編寫一個(gè)代碼長(zhǎng)度小于16KB的引導(dǎo)程序(以下簡(jiǎn)稱 uboot),其功能與DSP內(nèi)固化的Bootloader相同,用于加載最終的用戶代碼。在uboot程序中控制Flash存儲(chǔ)器的高位地址線來(lái)訪問(wèn) Flash的其他存儲(chǔ)內(nèi)容。這樣,DSP上電復(fù)位后,Bootloader首先加載uboot并運(yùn)行,然后uboot又加載最終用戶代碼,實(shí)現(xiàn)了大于 16K代碼的二次引導(dǎo)。

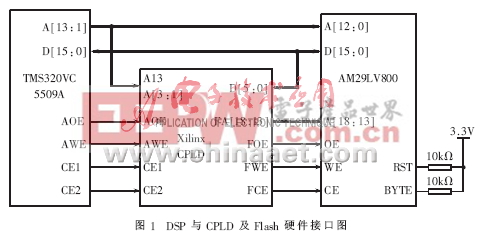

2.1 DSP與Flash及CPLD的硬件接口

本文采用AMD的 Am29LV800作為DSP的外部存儲(chǔ)器擴(kuò)展。Am29LV800按8位方式訪問(wèn),容量為1M字;按16位方式訪問(wèn),容量為512K字。DSP外圍電路邏輯譯碼及Flash高位地址線模擬由CPLD實(shí)現(xiàn)。Xilinx公司的XC9572XL是一款高性能的CPLD芯片,最高主頻可達(dá)178MHz,包含了 72個(gè)宏單元,1 600個(gè)可用門電路,其TQFP封裝有72個(gè)可用I/O引腳[7]。圖1是5509A與CPLD及Flash之間的硬件接口設(shè)計(jì)原理圖。本文引用地址:http://www.104case.com/article/152366.htm

如圖1所示,5509A的地址線A[13:1]與Flash的地址線A[12:0],A0未用。Flash存儲(chǔ)器被映射到DSP的CE1空間,由片選線CE1經(jīng)CPLD譯碼后選通。其中DSP的地址線A13和A[3:1]與CPLD接口,用于換頁(yè)寄存器FPR的模擬。Flash存儲(chǔ)器的BYTE引腳經(jīng)上拉后接高電平,即按16位方式訪問(wèn)。

2.2 CPLD譯碼VHDL程序設(shè)計(jì)

目前DSP系統(tǒng)主頻越來(lái)越高,運(yùn)算速度越來(lái)越快,利用小規(guī)模邏輯器件譯碼的方式已不能滿足DSP系統(tǒng)性能的需求。CPLD器件以其嚴(yán)格的時(shí)序、快速的譯碼、良好的可編程性成為DSP系統(tǒng)必不可少的部件之一。

本文利用CPLD的快速邏輯譯碼功能,模擬了一個(gè)FPR寄存器來(lái)控制Flash的高位地址線。VHDL語(yǔ)言源程序如下(篇幅有限,這里省略實(shí)體端口聲明及中間信號(hào)定義):

begin

fce =ce1;

foe =aoe;

fwe =awe;

h_addr =a13;

l_addr =a3a2a1;

datain =d5d4d3d2d1d0;

facs =′1′ when h_addr=′1′

and ce2=′0′ and l_addr='000'

else ′0′; --CE2 0x400000

FPR:process(facs,awe,reset)

begin

if reset=′0′ then

fa=″000000″;

else if reset=′1′ then

if awe′event and awe=′1′ then

if facs=′1′ then

fa=datain(5 downto 0);

end if;

end if;

end if;

end process;

dataout=fa when aoe=′0′ and facs=′1′

else ″ZZZZZZ″;

d5 =dataout(5);

d4 =dataout(4);

d3 =dataout(3);

d2 =dataout(2);

d1 =dataout(1);

d0 =dataout(0);

fa18 =fa(18);

fa17 =fa(17);

fa16 =fa(16);

fa15 =fa(15);

fa14 =fa(14);

fa13 =fa(13);

end behaviour;

由上述VHDL程序可知,F(xiàn)PR寄存器被映射到了CE2空間的0x401000地址。其中引入A13及A[3:1]地址線的目的是為了便于以后的功能擴(kuò)展,映射出更多的寄存器,如LCD控制寄存器、UART控制寄存器等。

評(píng)論