基于CH7004的嵌入式系統VGA接口設計

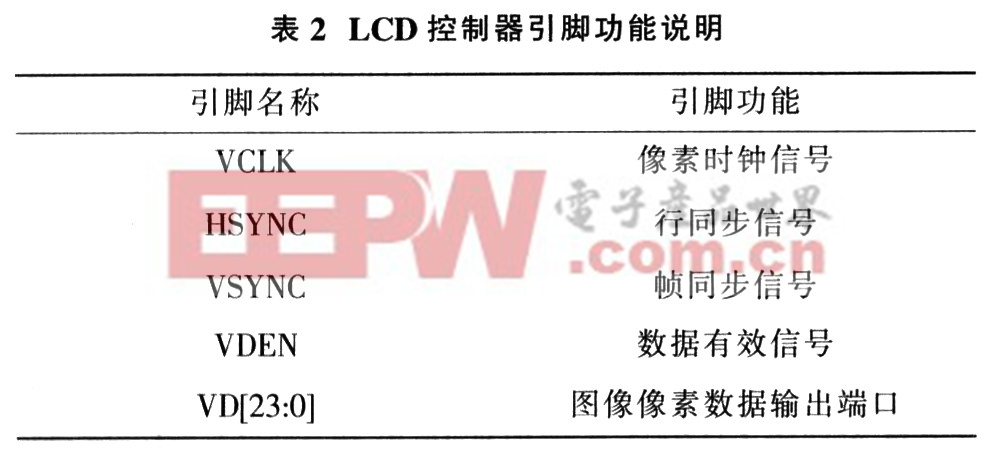

3.1.1 LCD控制器引腳功能

LCD控制器引腳分為時序控制端口和數據端口。與該設計相關的端口具體含義見表2。本文引用地址:http://www.104case.com/article/152325.htm

3.1.2 LCD控制器內部控制寄存器

LCD控制器內部有5個控制寄存器:LCDCON1~LCD-CON5。LCDCON1控制像素時鐘、掃描模式和顏色模式;LCDCON2控制幀同步脈沖寬度、幀有效行數及幀同步前、后的無效行數:LCDCON3主要控制行有效像素點數以及行同步前、后的無效像素點數:LCDCON4主要控制行同步脈沖寬度:LCDCON5主要控制行、場同步脈沖和數據有效信號極性,16位色顏色格式.數據輸出與像素時鐘跳變關系。

3.2 CH7004器件簡介

CH7004是Chrontel公司生產的一款數字轉換為模擬的視頻編碼器,其內部編碼器支持NSTL、PAL兩種視頻制式,通用數字輸入接口支持8、 12、15、16和24位數字RGB或者YCrCb格式輸入,支持5種圖像分辨率,內部集成3路相互獨立的高速視頻數模轉換器,可由用戶控制輸出模擬 RGB或YUV,提供I2C接口供用戶控制器件工作模式。

4 VGA接口設計

S3C2410處理器的LCD控制器用于產生圖像數據、VGA接口時序(640x480,60 Hz)以及配置CH7004的工作模式。CH7004將數字圖像數據模擬化,最終產生的模擬圖像信號供支持VGA接口的顯示器顯示。VGA接口的硬件連接見圖2。

這里選擇(640x480,60 Hz)模式,是由實際需要和硬件特性決定的:(1)嵌入式系統中的圖像尺寸大多低于640x480,采用這種VGA模式顯示不會丟失任何原始圖像信息; (2)VGA的每種顯示模式所要求的像素時鐘不同,而S3C2410內部LCD控制的像素時鐘由器件的主頻分頻而來,在各種分頻后的像素時鐘里只有25. 25 MHz(202 MHz主頻進行8分頻)與VGA模式中的(640x480,60 Hz)模式所要求的像素時鐘25.175 MHz最為接近,微小的像素時鐘偏差不會影響VGA接口顯示;(3)16位色情況下,(640x480,60 Hz)模式數據流帶寬為35.2 MB/s,因而不會堵塞S3C2410數據總線,不影響處理器的其他控制、數據處理操作。

CH7004的數據輸入端口D0~D15與LCD控制器的相應數據輸出端口連接,LCD控制器的像素時鐘VCLK通過XCLK端輸入CH7004內部, ADDR為低設置CH7004的I2C總線地址,為0x76。CH7004輸出端需考慮視頻信號阻抗匹配問題,否則會出現圖像重影、雪花、或邊緣有波紋等問題。

評論