基于CPCI總線多DSP系統的高速主機接口設計

2.2 設計思想本文引用地址:http://www.104case.com/article/152127.htm

PCI局部端的時鐘是66MHz,而DSP共享總線為100MHz,時鐘的不匹配會給邏輯設計提出很多時序方面的問題。另外,PCI局部端數據總線是32位,而SDRAM數據總線是64位,如何匹配數據寬度也是一個問題。而且PCI局部端和DSP、SDRAM在控制時序上也有很大差別。

圖1中顯示的是共享總線結構,DSP、SDRAM和FPGA都掛在DSP的外部總線上。DSP之間的通訊可以使用DSP總線;各個DSP訪問SDRAM時,也要選擇DSP總線;而且當主機訪問DSP通訊時,也會不可避免地使用DSP總線。因此不難得出這樣的結論:DSP總線將可能成為系統的瓶頸所在。所以在設計主機接口時,必須提高總線的使用效率,減少申請DSP總線的次數,每次申請使用DSP總線時都要盡可能多地傳輸數據。

在微處理器設計中,Cache被用來緩存數據、解決高速CPU訪問低速存儲器時的瓶頸問題。為了解決上述兩大問題,在FPGA的設計中也采用了類似Cache的結構來隔離不同總線間的傳輸。在Cache的兩邊有兩個狀態機來控制Cache的讀寫和總線數據的訪問。使用Cache后,DSP共享總線和PCI局部端總線將被去耦合,這樣可以使兩級總線的數據

吞吐量都盡量達到自己的峰值速度。FPGA內部有豐富的存儲資源,大塊的BlockRAM可以方便地搭建成Cache;而且Cache越大,越能提高主機訪問DSP和SDRAM的效率,減小占用DSP總線的時間,從而可以縮短DSP間通過DSP總線互訪時的等待時間。

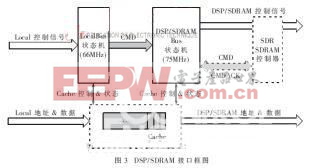

圖3是DSP/SDRAM接口框圖,都是基于雙狀態機加上Cache結構[2]。兩個狀態機同時監測Cache當前空、滿或是數據個數等狀態,以決定其動作;另外狀態機間還有命令通道,局部端狀態機用它向DSP/SDRAM端狀態機發出命令。由于這部分跨越了兩個不同頻率的時鐘域,因此必須加上同步電路以防止寄存器不定態的產生。

;

SDRAM接口與DSP接口不同處是它還有一個標準的SDRAM控制器,負責將自定義的SDRAM讀寫命令翻譯成SDRAM控制信號線RAS#、CAS#和WE#的組合。將SDRAM控制器獨立出來可以使得設計更加模塊化,避免SDRAM端狀態機過于龐大[3]。

2.3 DSP/SDRAM接口的實現

主機訪問DSP時,必須遵守DSP的流水線協議,其中重要的是讀寫時的流水深度:讀操作時流水深度始終為四個周期,寫操作時流水深度始終為一個周期。主機執行來自或去往DSP的突發操作時,支持超過四字的連續突發操作。當主機發出突發首地址,只要BRST#信號有效,DSP就在內部對地址累加。首次傳送的起始地址和最后一次傳送的結束地址必須四字對齊。這里只支持DSP端4字突發。

評論